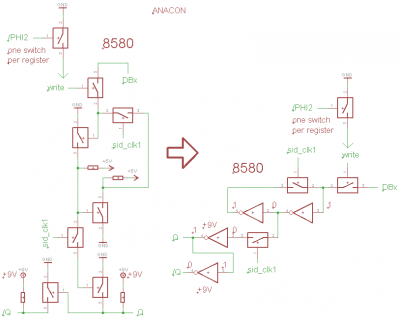

Now about the switches.

From the logic design point of view, the registers which control all the switches

and the filter frequency DAC all have identical schematics.

The layout for the register bits varies a little to make better use of the space

on the silicon, also size\geometry of the FET at the output might vary a little

depending on the load it has to drive...

Schematic for one register bit:

Attachment:

8580_anacon.png [ 15.55 KiB | Viewed 11059 times ]

8580_anacon.png [ 15.55 KiB | Viewed 11059 times ]

BTW: the PolySi write control lines are a bit long, so the designers added a FET to every 8 bit register

as a "kludge" to meet the bus hold timing that clobbers the write control signal to GND if PHI2 =0...

like with the registers in the envelope generator.

The game is similar like in the 6581... except for one thing:

each of the switches is built from two FETs instead of just one FET.

Attachment:

s8580_anacon.png [ 14.05 KiB | Viewed 11059 times ]

s8580_anacon.png [ 14.05 KiB | Viewed 11059 times ]

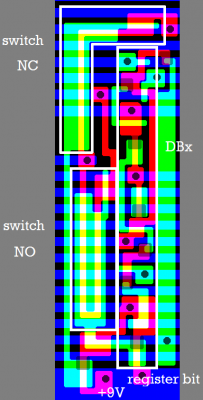

East, we have a big PolySi pad that connects to a bit on the internal data bus.

West, we have two analog switches,

one normally open (NO) // closed, if the register bit is written with 1

one normally closed (NC) // closed, if the register is written with 0

BTW: geometry\ratio of the FET that works as an analog switch gives the resistance of a closed switch.

...and in the middle, we have the register bit.

;---

In the 6581, we had one FET working as a switch for an analog signal.

In the 8580, we have _two_ FETs working as a single switch for an analog signal:

A FET with a low impedance and a FET with a high impedance in series.

IMHO this might be a trick from the designers to reduce capacitance between both ends of a switch.

The FET with the higher impedance tends to be at the side of the switch that connects to an OP or such...

Note, that this trick is also used in the frequency control DACs...

and maybe for resistors which don't act as a switch, too.