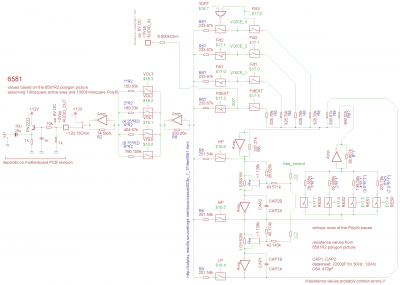

Tried to draw a schematic for the 6581 filter section:

Attachment:

6581_filt1.png [ 101.79 KiB | Viewed 10163 times ]

6581_filt1.png [ 101.79 KiB | Viewed 10163 times ]

Putting a voltage divider at the gate of the voltage controlled resistance FETs

is a trick to reduce distortion, I have seen something like that in CD4007 schematics.

Looks like the filter curve will go off with temperature.

Unfortunately, there was no space on the silicon to implement something like

a temperature sensor circuitry which modifies the voltage in the frequency control DAC

to compensate for this... but we are getting there later in the 8580.

;---

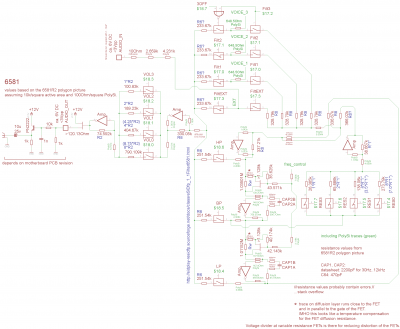

Also, I tried to calculate the resistance of the PolySi traces in the filter,

but at some point it became a bit too much, so please don't expect

all of those resistance values to be correct.

Attachment:

6581_filt2.png [ 127.55 KiB | Viewed 10163 times ]

6581_filt2.png [ 127.55 KiB | Viewed 10163 times ]

Anyhow, my reason for calculating the resistances of the PolySi traces only was

to figure out whether they might be big enough to be taken into account or not.

To put it this way:

For a true audiophile who had placed his amplifier on a 1 cubic meter marble block,

hand polished by blind virgins by full moon exactly to the micrometer,

all those resistances probably would matter.

On the other hand, Mr. Joe Average who happens to like Trash Metal

probably won't take a lot of those resistances into account...

just kidding.

BTW: the schematic doesn't include resistances of the metal traces.

When trying to add them later, please don't forget that metal traces happen to have

a different temperature coefficient than PolySi traces.