Since Drass is away for a while, I have tried to "translate" some of the results of our SID dissection into sort of a conceptual TTL schematic.

Pre_Farnell Eagle 6.4, because I happen to have the full version and I'm used to it (as in "drawing goes faster this way").

Attachment:

Edit: sid_main.sch, page 7:

Looks like something went wrong with the notation of the signal names: A0..A4, should be _A0.._A4, sorry.

Anyhow, it's only a "test balloon".

;---

Decided to aim for the 8580, because I lack some info for implementing the 6581 filter.

Nevertheless, resistor values in the waveform selectors are like in the 6581, take care.

Schematics are

_not_ verified, and I shouldn't try to do a verification because I'm too deep into these schematics.

Would be better to check if 'PHI11' and 'PHI22' are assigned correctly to the circuitry.

Schematics might contain some errors, and I wouldn't trust the envelope control circuitry too much.

Really, you better question/doubt anything in the schematics. Take them with a grain of salt.Couldn't resist "to try making the bus interface 20MHz", because we have that 20MHz TTL CPU.

Of course, the oscillator\envelope logic probably won't be able to go faster than 2MHz,

running the design with two phase_synchronous PHI2 clocks (registers 20MHz, oscillator\envelope 1MHz)

might create some _other_ problems...

...also, because there probably won't be enough PCB space for even thinking about double buffering the control registers.

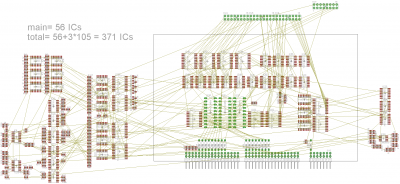

It's going to be a stack of four PCBs:

Three identical PCBs for the voices (oscillator + envelope + the related DACs), //3* 105 ICs

One PCB containing the bus interface, the filter and the rest. //1* 56 ICs

Since the schematics are not verified, it doesn't make sense to spend any thoughts yet on if/how that stuff might be going to fit on the PCBs,

371 ICs in total, have fun.

;---

Bus interface, with the wrong sort of connectors of course:

Attachment:

sid_main.png [ 187.94 KiB | Viewed 14171 times ]

sid_main.png [ 187.94 KiB | Viewed 14171 times ]

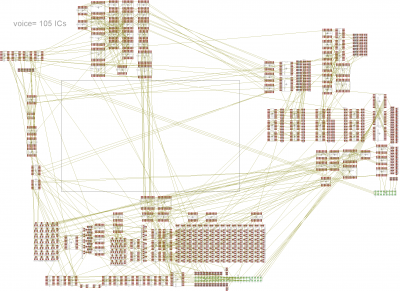

One voice, three such PCBs required. //Note the massive use of BAS40-05 and BAS40-06 Schottky diodes.

Attachment:

sid_voice.png [ 347.52 KiB | Viewed 14171 times ]

sid_voice.png [ 347.52 KiB | Viewed 14171 times ]

It's a beauty... at least to fans of

Boris Karloff.

;---

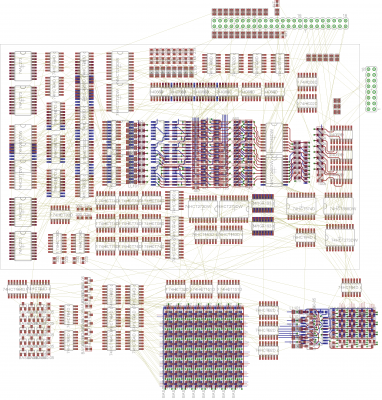

Edit:

After some tinkering with the 'voice' schematics and PCB layout, I would dare to say that there is no way to squeeze this into a 160mm * 100mm form factor.

I'm sorry to say this... but maybe we should spend some thoughts about an alternative concept.

Attachment:

sid_voice2.png [ 1.04 MiB | Viewed 13998 times ]

sid_voice2.png [ 1.04 MiB | Viewed 13998 times ]