Now for the bus interface.

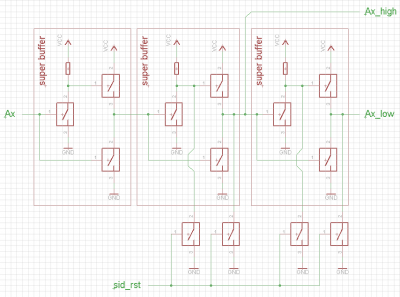

First the circuitry which generates the internal inverted and non_inverted address lines

Ax_low and Ax_high from the external Ax address bus.

It makes creative use of super buffers:

Attachment:

sid_ax1.png [ 19.72 KiB | Viewed 8197 times ]

sid_ax1.png [ 19.72 KiB | Viewed 8197 times ]

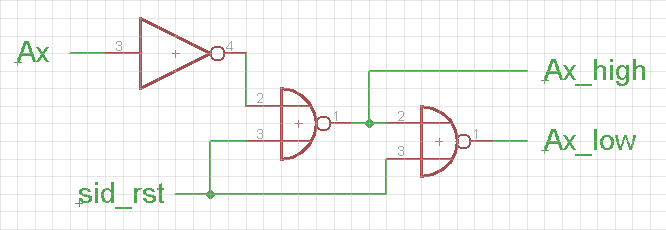

From the logic design point of view, it's something like this:

Attachment:

sid_ax2.png [ 6.83 KiB | Viewed 8197 times ]

sid_ax2.png [ 6.83 KiB | Viewed 8197 times ]

If sid_rst = 1, then Ax_high = 0 and Ax_low = 0.

Else, Ax_high = Ax and AX_low = /Ax.

;---

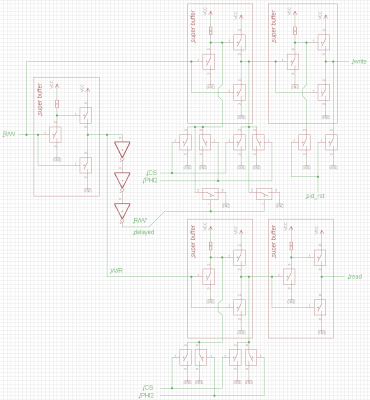

The circuitry which generates /read and /write also makes creative use of super buffers:

Attachment:

sid_csrw1.png [ 31.61 KiB | Viewed 8197 times ]

sid_csrw1.png [ 31.61 KiB | Viewed 8197 times ]

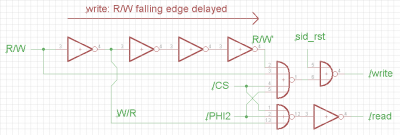

Logic design point of view:

Attachment:

sid_csrw2.png [ 13.22 KiB | Viewed 8197 times ]

sid_csrw2.png [ 13.22 KiB | Viewed 8197 times ]

For write cycles, the falling edge of R/W is delayed.

//Considering the C64 bus timing, it would be interesting to compare the 6522 and 6526 bus interface...

Note, that /write is forced to '0' if sid_rst = 1.

When taking a look at the data bus buffers later, it becomes evident that the internal data bus

is forced to $00 while sid_rst = 1.

So during a RESET, if sid_rst = 1, all the NOR address decoder gates tied to /write

will go active because all their address inputs are 0.

This forces a write of $00 into _all_ of the registers that could be written from the bus.Nice trick.

;---

Now a code snippet from vice 2.4 > resid > resid.cc

Code:

// Write registers.

// Writes are one cycle delayed on the MOS8580. This is only modeled for

// single cycle clocking.

// ----------------------------------------------------------------------------

void SID::write(reg8 offset, reg8 value)

{

write_address = offset;

bus_value = value;

bus_value_ttl = 0x4000;

if (sid_model == MOS8580) {

// One cycle pipeline delay on the MOS8580; delay write.

write_pipeline = 1;

}

else {

// No pipeline delay on the MOS6581; write immediately.

write();

}

}

But after dissecting the bus interface circuitry of 6581R3 and 8580R5,

I'd say that the bus interfaces just have different geometries,

but they seem to be identical at transistor level from the

logic design point of view.

In other words: we were unable to find any proof that there might be something

like a one cycle write delay on the 8580.

;---

Also, vice 2.4 resid source code implicates, that when writing a register,

the byte also stays on the internal data bus, and if you try to read a register

that can't be read you are just "getting that byte back".

But after $2000..$4000 clock cycles, bits that were 1 on the internal data bus

are "fading" to 0.

BTW: don't get confused by the overly simplified schematics from the logic point of view above,

they are just there to show how things are working in general.

Trying to build a 6502 compatible bus interface for a peripheral chip can give you some grey hairs,

especially when trying to aim for speed.

When I did an experimental TTL implementation of the 6522... but I'm getting off topic.