The remaining LFSR mysteries...

Putting that three_input OR gate in front of the XOR gate which feeds the LFSR input

certainly won't do for properly initializing the LFSR.

The OR gate would have to be placed between the XOR gate output and the LFSR input,

but I think this would have required a little bit more space on the silicon.

Of course, "the professional approach" would have been to implement a 23 input

NOR gate to force the LFSR input to 1 if all the LFSR flipflops are 0,

but there certainly wasn't enough space on the silicon for something like that.

So in my opinion, whoever did the logic design for the

SID was well aware

that the LFSR bits would be turning from 0 to 1 after a while...

;---

Edit: more than two months had passed by since writing this post.

My theory of a "hidden P FET" turned out to be pure nonsense, so I deleted it.

But we still have no clue, what brings the LFSR bits back to '1'

after they were '0' for some time.

1) There is nothing in the transistor level logic design that could explain this effect.

2) When comparing 6581 and 8580, bits seem to go '1' in different order.

// Connections between LFSR and wave selector are wired up identical for both chips, checked this.

3) Effect depends on chip and on temperature.

4) There is nothing "suspicious" in the pictures of the 6581 and 8580 silicon.

Whatever it is, it probably is a trick hidden in the manufacturing process of the silicon or such.

With the info and the skills we have now, we can't solve this riddle.

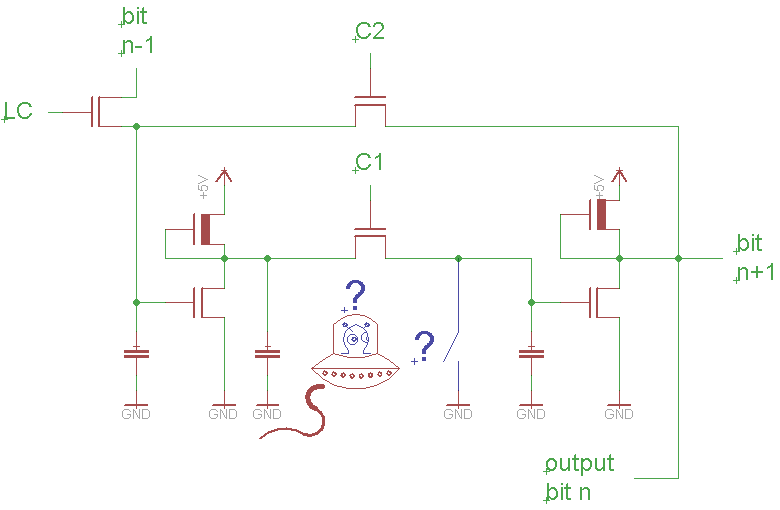

Attachment:

lfsr_foo.png [ 7.66 KiB | Viewed 6825 times ]

lfsr_foo.png [ 7.66 KiB | Viewed 6825 times ]