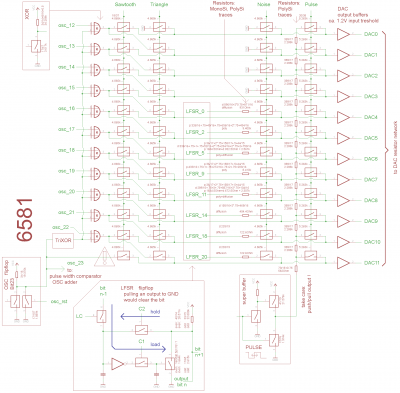

6581 waveform selectors again.

Attachment:

6581_waveselect_ohm.png [ 120.01 KiB | Viewed 5230 times ]

6581_waveselect_ohm.png [ 120.01 KiB | Viewed 5230 times ]

Tried to calculate the resistance values of FETs and traces,

assuming that PolySi has 100 Ohms / square.

From the book:

Code:

Metal ca. 0.1 Ohms / square

Diffusion ca. 10 Ohms / square

Poly ca. 15..100 Ohms / square

Transistor ca. 10k Ohms / square

Omitted the resistance values of the metal traces,

because they would be 4.2 Ohms or less.

Also, I omitted the Diffusion traces between the selector switches,

because having them in the schematic above wouldn't have increased readability...

Attachment:

6581_waveselect_sw.png [ 20.3 KiB | Viewed 5230 times ]

6581_waveselect_sw.png [ 20.3 KiB | Viewed 5230 times ]

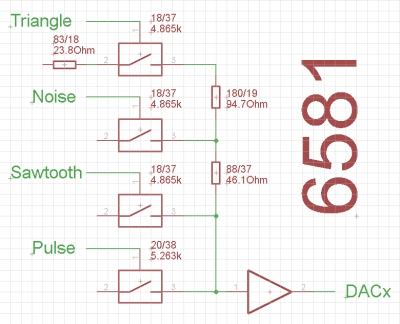

All the values are roughly estimated "house numbers" for the 6581R2, of course,

and I'm not sure all of those values might be correct.

Would suggest that somebody spends some weeks with dissecting the layouts

of the other 6581 revisions and the 8580 to extract the exact resistance values.

BTW:

When comparing different 6581s, there might be some tolerance in the resistance values.

Tolerance might be bigger when comparing 6581R2s from different batches.

And it still might get bigger when comparing different 6581 revisions.

But I think that for an initial simulation of the waveform mixing effects in a 6581,

the stuff above might do.

;---

Basically, when mixing waveforms, we have resistors to GND and resistors to +5V

(the FET transistors at the outputs of a gate or a flipflop),

and resistors in between (the traces on Poly and Diffusion layer etc.).

For the DAC buffers and the LFSR flipflop inputs, threshold voltage

(turning point from logic level low to logic level high)

is supposed to be ca. 1.2V.

What voltage really is there depends on the resistance values...

but we could suppose, that the bigger the resistance of the traces,

the less good mixing the waveforms may work...

German wikipedia says, that the 8580 was manufactured with a HMOS II process,

and that HMOS II is 2 micrometers (with a typical propagation delay of ca. 30 ns per logic gate.)

https://de.wikipedia.org/wiki/MOS_Technology_SIDhttps://de.wikipedia.org/wiki/HMOS6581 had 7 micrometers, so the traces in the 8580 might have 3.5 times

the resistance value of the traces in the 6581, while resistance value

of the FETs for both chips probably would be similar.

...So I guess that mixing waveforms on the 8580 "would sound less impressive"

than on the 6581.

;---

Edit1: Added resistor values to the switches, thanks to BigEd for pointing this out.

Edit2: Pulse selector switches have slightly different geometry, thanks to drfiemost for pointing this out.

Edit2: Added wikipedia link to HMOS II.