JohanFr wrote:

There is a glitch, but according to the specification it is only relevant for speeds over 18 MHz. I am running the circuit at 1.5 MHz so in theory it shouldn't[tm] be an issue. I tried to use 590's in the beginning but found the double clock annoying and couldn't really get it to work satisfactory. Now it seems to be mostly working so I am hesitant to tear it apart a fourth time

(this is the second '163 build, previously also built one '161 version and one '590 version

)

Yeah, the 590 register can be kind of a pain. Sure is nice to only have 2 counter ICs per EPROM rather than 5 or 6 though!

Quote:

The series resistors is a "i read it at some random forum that you should put some 47 ohm:ish resistors on sync signals" addition. They make no apparent difference what I can see so I might remove them again.

Aha! LOL! I was just curious; I've never seen those before.

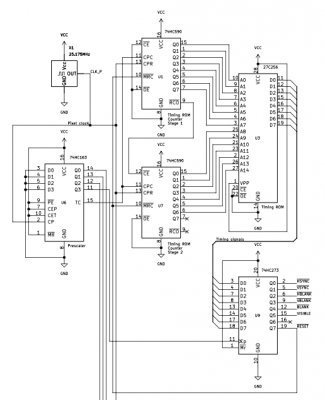

Here's the timing side of my VGA board. It's very similar to George's. I added a few signals, because my output side is different (using a character ROM to generate a text-only display).

Attachment:

Screen Shot 2024-05-18 at 12.50.41 PM.png [ 69.37 KiB | Viewed 80 times ]

Screen Shot 2024-05-18 at 12.50.41 PM.png [ 69.37 KiB | Viewed 80 times ]

VGA is kind of simple, in a way. There are really only two problems you can have. If your timing signals (HSYNC, VSYNC) are out of spec, the display won't lock *at all* and you get nothing. You clearly are not suffering from this problem.

If your timing signals are good, then the display will - mindlessly - present whatever comes in over the RGB lines. (This is assuming your display is a good one - hopefully by now you plugged it into something else to make sure it actually works!

) That means that *the display itself* is a kind of debugging of your output side logic.

In your picture, I see 40 columns that are good for a few scanlines, then each scanline gets off by one more pixel every line until everything has moved over more than one column, and then it *moves back the other way* a pixel at a time, but not every scanline, until it settles in and remains stable for the rest of the frame. I'm not sure which area is the correct one - do you expect to see a green bar or a black bar in the first column? Either way, this seems an awful lot like an out of phase counter.

Looking at your output register, it's clocked by SCLOCK, which is ~1.57 MHz, and reset by DISPLAY. I'd take a look at those two signals in addition to checking to make sure your timing ROM is correct. One thing you might try is setting the whole screen to white. Any irregular black areas will tell you about your front / back porch and blanking timing. Also, what happens if you never reset the output register? (This will show you exactly where the monitor thinks each frame begins and ends.) Or, what happens if you don't use the output register at all? (Just tie RGB high through resistors.) Do you get a square, or do you still see distortion?

Etc.