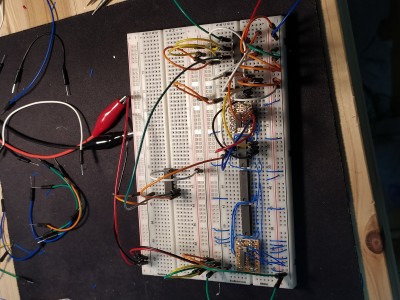

Well, in between painting this, and laying a floor that, and carrying boxes the other... I managed to knock together a little bit of test hardware. And, woohoo, the SVGA line timing works and is spot on... though the circuit looks like it was put together by an inebriated spider...

Attachment:

1703792192139.jpg [ 4.05 MiB | Viewed 834 times ]

1703792192139.jpg [ 4.05 MiB | Viewed 834 times ]

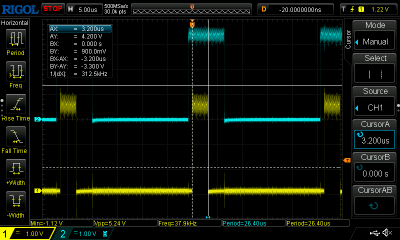

Line sync is 3.2us:

Attachment:

DS1Z_QuickPrint21.png [ 56.74 KiB | Viewed 834 times ]

DS1Z_QuickPrint21.png [ 56.74 KiB | Viewed 834 times ]

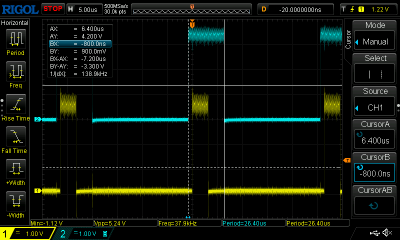

Line blanking is a touch longer than spec; I'm using only 384 of my 400 horizontal pixels:

Attachment:

DS1Z_QuickPrint22.png [ 57.01 KiB | Viewed 834 times ]

DS1Z_QuickPrint22.png [ 57.01 KiB | Viewed 834 times ]

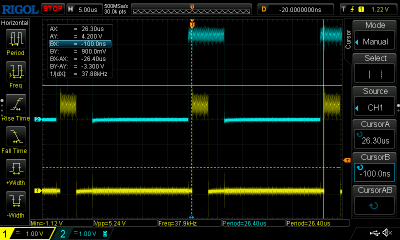

And the line timing is exactly 26.4us:

Attachment:

DS1Z_QuickPrint23.png [ 56.1 KiB | Viewed 834 times ]

DS1Z_QuickPrint23.png [ 56.1 KiB | Viewed 834 times ]

All this in just six and a bit chips (there's a seventh chip in there to generate the load pulse for the parallel to serial chip, but I didn't count that

) and it's perhaps interesting in that it uses - after the initial 20MHz tp 2.5MHz divider - ripple counters and decoders. The count always increments in such a way that there aren't any glitches that affect the outputs.

The field generator works in a similar, but not identical, way, so that's next to check if it fits on the board.

Neil