reading the board, wikipedia and GARTHWILSON's detailed works, especially here:

http://wilsonminesco.com/6502primer/IO_ICs.htmlthe existing datasheets and other sources I have more questions than answers.

we are primarily interested in current production chips

all of these chips in CMOS versions are at least:

Static to 14MHz and Bus compatible with 14 MHz W65C02S and W65C816S

Static to means it can stop and hold its state and be stable 'up to 14MHz',

and it is able to share a bus with 65xx cpus okay.

come in a 40 Pin Plastic Dip and can run on a 5V Power Supply

It can fit on a breadboard and use 5v rails.

______________________________________________________________________________________________

6521 PIAhttps://www.westerndesigncenter.com/wdc/w65c21-chip.phphttps://www.wdc65xx.com/wdc/documentation/w65c21s.pdfhttps://en.wikipedia.org/wiki/WDC_65C21Features:

2 x 8−bit bidirectional I/O ports with individual data direction control

Automatic "Handshake" control of data transfers

2 Interrupt outputs with program control

so there seems to be very little use of this or projects employing it. I read "two 8-bit parallel ports". This lends me to think of this as an 8 or 16 bit mono- or bi-directional parallel port, and in my head, that says 'printer port' though I know this is not the same thing as an IEEE 1284 port/cable/whatsit. (20 years since I needed to know that.) There is a shortage of usage of this circuit which seems to require a lot of extra support hardware, like timers?

so, the PIA also looks to be the oldest of the chips in this set, and mostly not so great, it seems like the VIA chip, it's successor is better in everyway,

except the 6522 has a bug in it. In fact, although his chip has no timers or other features, it also is seems to be "bug free".

This chip will at least need timer circuitry and maybe latches to start doing what other chips can do. Is there any practical reason to employ the PIA '21?

personal note wrote:

I have located a small LCD module that is 1/5th my later display size, with 4 bit gray. It uses an ST7528P, which seems to be in either 8080 or 6800 parallel modes. very interesting.

______________________________________________________________________________________________

6522 VIA

https://www.westerndesigncenter.com/wdc/w65c22-chip.php

https://www.westerndesigncenter.com/wdc ... 65c51n.pdfhttps://en.wikipedia.org/wiki/WDC_65C22this seems a little newer and has the same features as the 6521, except it also has timers,

some handshake/syncing functions, is explicitly 8 and 16 bit, has Latches on its I/O, can work

with TTL circuits, and it can run on variable voltages.

2 x 8−bit, bi−directional peripheral I/O Ports

2 x 16−bit programmable Interval Timer/Counters

Synchronous Serial bi−directional peripheral I/O Port

Enhanced "Handshake" feature works with either 8− or 8/16−bit systems

Latched Input/Output Registers on both I/O Ports

Programmable Data Direction Registers

TTL compatible I/O peripheral lines

1.8V(W65C22S only) − 5V Power Supply

Quite impressive indeed, except that...

it has a bug in two of its serial modes, see here:

http://forum.6502.org/viewtopic.php?p=2310#p2310Now from what I am reading, this can be resolved with a tiny flip-flop and running to the clock pin on the cpu...

the datasheet says for the cmos version, you need resistors, so, you will need as much or more support hardware here, as with the '21 PIA. However, this seems to be a 'workhorse chip' on many designs and possibly worth the extra effort, it truly is a

versatile chip.

However, we still have not explored the 6551 chip, the more advanced comms chip in the family.

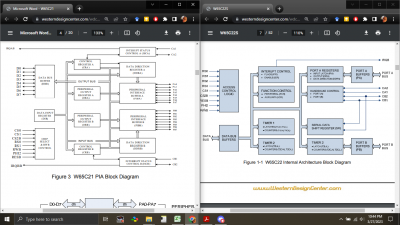

Comparison of 6521 and 6522 chips:

Attachment:

image.png [ 224.54 KiB | Viewed 20212 times ]

image.png [ 224.54 KiB | Viewed 20212 times ]

______________________________________________________________________________________________

6551 ACIA

https://en.wikipedia.org/wiki/WDC_65C51

https://www.westerndesigncenter.com/wdc ... n-chip.phphttps://www.westerndesigncenter.com/wdc ... 65c51n.pdfthese seem to be the most powerful of the chips available, until you take a closer look and realize it does not have parallel transmit line

per se, it has modem control functions and is basically

serial only.

Full duplex operation with buffered receiver and transmitter

Data set/modem control functions

Internal baud rate generator with 15 programmable baud rates (50 to 19,200)

Program−selectable internally or externally controlled receiver rate

Programmable word lengths, number of stop bits and parity bit generation and detection

Programmable interrupt control

Program reset

Program−selectable serial echo mode

2 Chip Selects

So this chip is not more or less powerful than the other two, it actually does different things. It is basically a very low level modem/modem controller and seems really very gear towards the RS-xxx series of protocols, and could be used for several others.

I am uncertain what this chip can really do alone, though coupled with a 6522, it seems very versatile at sending and receiving data.

It appears this chip as well has some hardware errors and may need workarounds or a recall.

https://github.com/andrew-jacobs/w65c81 ... 6sxb.inc-1______________________________________________________________________________________________

Beyond this are many other options for CPU I.O that are not in the 65xx family of ICs.

We will explore these and the primary protocols in use todays and start identifying possible choices in our next post.

Any errata , corrections or other info in replies will be consolidated here or below.