I'm trying to do some prototyping with 8088 (actually, with KM1810VM88 which is a clone of 8088 that was made in Kyiv, Ukraine during soviet times), and due to my familiarity with 65xx family, I'd like to use 6522 VIA as my I/O controller.

There are several problems:

- 8088's clock is asymmetric (2/3 cycle low, 1/3 high) - I don't think it's an issue for CMOS VIA, right?

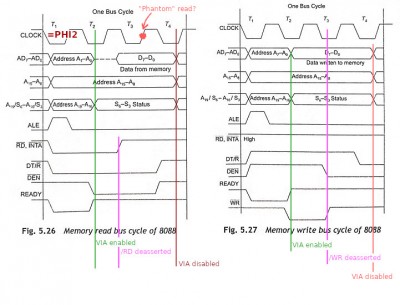

- 8088 doesn't sync /RD & /WR in the same way that VIA expects it to be synced with PHI2 input: it looks like 8088 will assert /RD & /WR (as well as address) for more than 1 full clock cycle, thus enabling it across multiple VIA PHI2 cycles.

Attachment:

via.jpg [ 88.96 KiB | Viewed 4258 times ]

via.jpg [ 88.96 KiB | Viewed 4258 times ]

Now, from W65C22 datasheet:

Quote:

The system PHI2 Input Clock controls all data transfers between the W65C22 and the microprocessor.

Questions:

- Does that mean I cannot read/write VIA without aligning my reads/writes with PHI2?

- As long as VIA is enabled, does it still hold the data bus (during reads) for subsequent PHI2 cycles?

- How exactly does VIA use PHI2 (besides counters)? Does it gate PHI2 with R/W?

Worst case which I think can happen is double reads/writes to/from VIA, which is not critical for me. Are there any hidden caveats that I'm missing?

P. S. I know most 80xx CPUs come with optional controller chips (and there's probably one for I/O as well), but I want to build all the glue logic by myself without resorting to Intel's chips.

EDIT: I think there are more issues on the way, since I don't think VIA will hold data long enough (i. e. for more than 1 PHI2 cycle) for 8088 to sample it.

But once I start adding latches to help 8088 talk to VIA, I'll end up having too much glue logic. I guess I'll have to use a different chip that's not as dependent on clock as VIA.

EDIT 2: I could simply use "/RD AND /WR" as PHI2 input to get correct timings, but then I'll lose VIA's timers.

EDIT 3: Is anyone aware of any alternative parallel I/O chips similar to VIA but not reliant on clock signal - i. e. strobed by /RD & /WR?

_________________

/Andrew

deck65 - 6502 slab with screen and keyboard |

ПК-88 - SBC based on KM1810VM88 (Ukrainian i8088 clone) |

leo80 - simple Z80 SBC

nice65 - 6502 assembly linter |

My parts, footprints & 3D models for KiCad/FreeCAD