Thanks for the suggestions!

I've looked into the NOR circuit in more details, and built a timing diagram for it. Considering the use of an AHC02 and our pseudo-RDY changing during the low phase of the input clock, we get this:

Attachment:

Screenshot 2023-08-04 at 16.18.22.png [ 554.3 KiB | Viewed 583 times ]

Screenshot 2023-08-04 at 16.18.22.png [ 554.3 KiB | Viewed 583 times ]

It looks like it works well for stretching. Timing is a bit tricky because if it happens to go low when the source clock is already low, a partial PHI2 low is generated (see fourth cycle above).

So, it needs to only change during the high phase of the source clock. Presumably up to right before the edge. I'm not sure if two logic inputs could have different propagations, ie should RDY be setup some nanoseconds before CLK or is 0ns acceptable

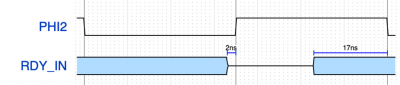

Assuming 0ns is, this is what it looks like from the point of view of Q/PHI2

Attachment:

Screenshot 2023-08-04 at 16.36.30.png [ 75.52 KiB | Viewed 583 times ]

Screenshot 2023-08-04 at 16.36.30.png [ 75.52 KiB | Viewed 583 times ]

So it would need to be stable from 17ns before the falling edge of PHI2, until 2ns before the rising edge of PHI2.

Note that this assumes a very worst case of everything taking either the maximum time to propagate, or the minimum, depending on which edge we're at. In the real world there wouldn't be these massive swings on two consecutive edges for the same IC... But the result is still the same, it needs to be stable a bit before and during PHI2 low.

This is where I'm at, I haven't looked in details into the thread you linked yet, but I will keep thinking about this!