fachat wrote:

Good you found the '273 because of its reset capability.

[...]

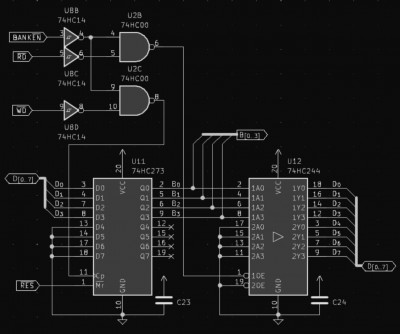

Is /banken qualified with phi2? Otherwise it stays valid for too long, and the CPU has taken the data off the bus already

IIRC the 273 latches the data in at rising edge of CP. So you should make sure CP is only low when phi2 is high.

Yep, it is: I have used /RD & /WD signals (qualified with Ф2) as inputs in my latest design, since I already have them in my SBC. I also happened to have just enough spare '14 gates for this task:

Attachment:

rw_banking3.jpg [ 101.46 KiB | Viewed 4559 times ]

rw_banking3.jpg [ 101.46 KiB | Viewed 4559 times ]

gfoot wrote:

It would be easier if you didn't allow reading the register. You can cater for that by having a separate RAM location that code had to update just before changing the hardware register (which is what Acorn did in the BBC Model B, though they provided a readable register in the later Master models) or you can have the hardware register overlay/shadow a RAM address, so that writing the RAM address also writes the hardware register.

While I agree that it would eliminate the need in '244, I still prefer to use it for two reasons: it gives me satisfaction to do hardware solution for this and it also eliminates the need to track a copy of last written value in RAM.

fachat wrote:

What you need to do is to provide the ability, from kernel mode, to read (and sometimes write) data from (into) the user process. For example reading a file name to open a file is more efficient if the filesystem process can read it from some mapped user space. (you could transfer the name etc using a byte-based protocol with a kernel call per byte, but that is highly inefficient.) Also for reading and writing mass data (like loading a file) the kernel should be able to read from or write to user space.

Yeah, it seems like it would be nice to have an ability to map different regions of multiple banks at once, especially when there's a need to copy data between processes, or work with kernel & user-space data simultaneously.

Another option I can think of is to use "swap" memory for this purpose, e. g. during some syscall, a kernel would copy data from bank 1 into this area, then switch to bank 2 and copy the data there.

But I think most of this copying can be minimized if all program-related data (file descriptors, buffers, etc) is to be stored in program bank. In other words - make kernel use program banks as much as possible, and use kernel's own bank only for metadata (process list, etc). This way each program will "own" most of its data locally. There are some complications though: a program should never touch those kernel-managed data regions of its bank, and mutate them only via syscalls. And, of course, copying data between banks will be very slow.

André - would you mind providing some link or code for your call buffer feature? It sounds interesting and I'm really interested in understanding how it works. Is it just a shared region of memory to be used by multiple processes to transfer data between banks, or something more complex?

_________________

/Andrew

deck65 - 6502 slab with screen and keyboard |

ПК-88 - SBC based on KM1810VM88 (Ukrainian i8088 clone) |

leo80 - simple Z80 SBC

nice65 - 6502 assembly linter |

My parts, footprints & 3D models for KiCad/FreeCAD