Project "Integrity"

Standalone Core Screen UnitAttachment:

bitmap.png [ 171.5 KiB | Viewed 1960 times ]

bitmap.png [ 171.5 KiB | Viewed 1960 times ]

Quote:

“A late game is only late until it ships. A bad game is bad until the end of time”

Shigeru Miyamoto

This is a long time project of mine I have been working on here and there since the 90s when I was a kid holding a cordless phone in my folk's kitchen. This is a modular portable device comprised of various units:

Financials and Open Hardware StandardsExpected Cost for the Core unit is expected to be $250-350 USD.

This includes ICs, PCB, Assembly, Screen, Battery and Shipping, as well as a margin for unexpected costs.

This number is a goal as much as an estimate, though so far we are in range. At no time shall we exceed $450 USD.

Projected Production is in 1-10s of units during development, unless externally funded.

Our goal is a run of 10,000+ Units ideally crowdfunded with pre-orders.

The specification, OS and software are largely Open Source and can be user repairable or assembled.

The Integrity from Wayfarer Technologies is a device, an Integrity, or "One's Integrity" need only conform to the specification standards.

Waytech would only directly offer customer support for the Wayfarer Technologies Integrity Mobile Computer, the community might support DIY users and 3rd party developers.

Several Peripherals are planned and offer vectors for future development or expansion. including Industrial and Scientific Computing Modules for business and education, audio modules for interfacing with recording and performance equipment, and a keyboard for development and typing. Radio communications modules and PCMCIA adapters allow for use of thousands of existing devices extending their usefulness. Hardware that conforms to the Integrity standard specification should have interoperability with any of these peripherals.

Operating SystemIntegrity OS <working title>

link: TBD

an 8/16-bit mixed use OS for mcu/mpu computing and development

runlevels for 8 bit 6502 work on

65816 in e-mode

runlevel 0/1 is recovery/examination/boot mode

higher runlevels for 'unlocked' hardware access or 16-bit mpu or modes (native mode)

this means the 'BIOS' ROM code, is the recovery/rescue mode code, and is the basis of the 8-bit version of the OS

when the

65816 is in 'e' mode, the OS specification calls for the lower runlevels to restrict the hardware registers to 8-bit lengths wherever possible to provide the same interfaces to the hardware, ie, 6502 software will run on the chip as expected, and

65816 software written to this runlevel spec will then run on a 6502, barring compiler options for manufacturers, type C vs type N processes etc.

Core:

Screen ~8-8.5" 800x480 WGA variable backlit LCD

Power 5+v Battery Pack or 4x 1.x Volt Cells,

Charging Unit and Jack, charger runs from USB(-C?) and any other 5v+ in sources,

USB ICs include the Max301/300 series/Max2000, 7795b, STUSB1602 etc

while 20v going near the cpu is 'scary', it should be isolated enough, there is a goal to keep power at 5v max, use an earlier or alternate standard, which offer locking industrial grade connectors, still. usb c, and usb-otg are supported and useful features

20v exceeds 12v, which allows flashing of EEPROMs and other high voltage tasks. As this is only supplied when plugged in, it may be acceptable. if so, overvoltage protection, a circuit breaker, or dedicated redundant overvoltage protection is desired if not required.

even at this point, using sockets for replacing a damaged chip becomes a choice.

5v, 3.3v are the main voltage 'rails' we are using, with a possibility of a ~1.8v rail or local voltage modification

Given that we are using PCMCIA Type-1 as a multi-port, 5v and 3.3v are required.

A few WDC chips will need 5v for 12Mhz stability, out current middle buss speed. Most ICs however will operate on the 3.3v rail or plane.

Regarding EOMA68, this well intentioned idea is hazardous due to incorrect pinouts (or documentation?). every effort will be made to detect the EOMA68 cards, reject and lockout any power on those cards, including sending shutdown signals to them until removed. These are dangerous to every computer they touch, because they failed to respect and adhere to existing standards.

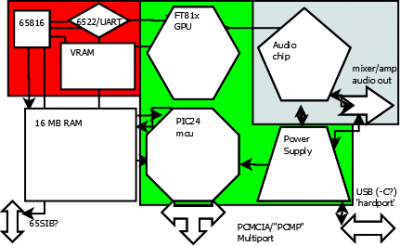

CPU Logic Unit 16-Bit

65816 @12/4 Mhz (or 8/4? tbd)

this is the frontal cortex of the system, the steering and driving chip that is most directly programmed by the user or developer.

in

e mode, the system will be intentionally constrained at the appropriate OSI layer, as a specification point, it is intended here that the X, Y registers be in 8-bit modes when not directly being used for 16-bit tasks, being returned to 8-bit modes afterwards. (this probably needs clarity). A low clock for the 6502 emulation mode and low speed communications may be provided by an additional clock or a clock divider circuit.

Math Co-Processor Micromega u-FPU v2 or v3, PIC33 DSP or similar

Local I/O Unit 6522 VIA chip? (or alternative micro UART chip such as MAX3100 series)

the local I/O chip is basically optional, the PIC is going to offer an order of magnitude more connectivity and utility out of the gate, it's what it was designed to do. However, in early startup, low runlevels, recovery, debugging etc; it is desirable to examine and interact with every piece of hardware, every bit. Further, having direct access to the possible 65SI Bus/65SIB connector from this UART/support I/O chip to the CPU in the CPU core section of the board with some dedicated RAM and recovery ROM does offer a 'backup and recovery system' to unbrick the device and interface with other machines. It may be possible to not include this chip or unit, and it may create a complicated layout or OS routine to support such low level redundant I/O with a PIC24 acting as a full RIOT-esque chip. However, it does offer an extra channel or two of communication, bypasses the PIC and should support the 65SIB connector, and may allow terminal type access to the CPU, the onboard ROM and allow system recovery and updates, especially if the PIC requires updates or repair.

Attachment:

Function Draft 2.png [ 19.88 KiB | Viewed 1697 times ]

Function Draft 2.png [ 19.88 KiB | Viewed 1697 times ]

System Busses and Support ComponentsHigh Speed Video Bus 60 Mhz, GPU, Flash Memory i/o, the GPU has a 12.000 Mhz internal or external clock and a multiplier/divider

Mid Speed Common Bus 12 Mhz, PIC24 can run at up to 16 or 60depending on model, it at 60, it will bus to the GPU. The

65816 will also run at 12. Mhz in this case if the current GPU, a Bridgetek FT816 is used, to better sync up to its clocks and minimize oscillators.

RAM is being considered in full SRAM, dual port VRAM and traditional DRAM options. The system will have 16 MB of RAM, and may have additional RAM via a switch or RAM banking, allowing for 64MB of available RAM or More. the Integrity OS specification will further determine this. A major consideration is using high speed battery backed SRAM in 64K for the 6502 e mode to use as a dedicated 'fast page' or similar configurations regarding core functions of the 65c02/

65816 in e mode.

RAM banking, fast ram for local pages banks, extended ram and rom chip options are being explored. The 6505/

65816 have MMIO addresses for dedicated video access and control, mapping this to shared vram or FIFO buffers etc may be desireable to achieve GPU control without going through the PIC/board controller or even the 6522.

North Bridge Multimedia Controller Bridgetek EVE 24/32-Bit LCD Controller @60Mhz (or lower?)

offers LCD driver, GPU, mono sound engine, touch screen and flash rom access

South Bridge Board Controller PIC 24E series 16-bit MCU @60 MHz (or 12?)

UART, Timers, Interrupts, SPI, I2C, ALU, and USB services

Sound Generator Savage Innovations SSG01 Soundgin (or Yamaha FM-Synth or Similar, a PSG chip)

Mixer, Stereo, Amplifier, Headphone Out, On-board Speaker or speakers.

Stylus ERM stylus reporting on a resistive touch channel to North Bridge

Multiport external bus adapter (PC-Card type I or ISA Pin-compartible), USB-OtG

we are directly competing with EOMA, a well meaning but physically incompatible use of PCMCIA.

we are extending/forking the legacy PCMCIA standard, itself descended from the venerable ISA standard, into what we are calling:

PC-Card Multi-Port, or PCMP and it is pretty much PCMCIA as of revision 2.1 or later, possibly to include the entire 32-bit CardBus with DMA, though type i 8/16-bit cards are enough for now.

Controls volume, mute, reset/hardware interrupt;

. D-Pad, Face Buttons, Triggers, analog stick may be on external "Grip" unit.

. the 8-bit D-Pad, Confirm, Cancel/Back, Option/Select and Start/Menu buttons are standard on all Integrity Cores

. power, volume+/-, reset button calls hardware ROM recovery mode code direct to CPU for debugging.

KeyboardKeyboard Unit with additional peripheral interfaces, rs-232, etc

MIDI Production Unita 24-Key weighted keyboard,

wavetable, midi connectors, amplifier hookups

drum pads

drone generators

wave form generators

metronome, microphone and headphone jacks

Data Sampling UnitMultimeter Leads

Thermocouple Lead

ADC/DAC

Signal and trace generators

Oscilloscope software

Scientific Graphing Calculator Keys

Backpackclip on shell

extra battery

extra PCMCIA slots (2 or 3)

screen cover folds to make kickstand

EarthshakerBallast class battery

Bass reflex tubing

multi-speaker array

mass storage array (flash for media?)

carry handle and accessory case integrated to unit

this unit can play MP3 or Ogg etc.

it has a small segmented or dot LCD, guitar jacks, etc

Spine and BinderSpine is a simple interface strip and housing that links two units together in the form of a book

Binder is a portfolio-esque case that can hold two units with a spine or keyboard and unit.

SketchpadE-ink display module, greyscale, 4 or 16 tone, highlight, tint or multicolor possible

compatible with Spine and Binder, possible overlay model uses thin film to rest over Core screen as a cover.

uses the same stylus, can 'flash save' drawings and notes to the Core.

WindtalkerRadio/Ir module

CB/Packet Radio,

Local Net/Wi-fi (WPA or WEP 16-bit), etc

Universal Remote

Images and Concept ArtStandalone Core Screen UnitAttachment:

bitmap.png [ 171.5 KiB | Viewed 1960 times ]

bitmap.png [ 171.5 KiB | Viewed 1960 times ]

With "Grip" UnitAttachment:

bitmap2.png [ 217.49 KiB | Viewed 1957 times ]

bitmap2.png [ 217.49 KiB | Viewed 1957 times ]