Hi everyone,

I was not sure whether to post this here or in Programming, but here goes.

I am trying ( and so far failing) to reliably read data from a CF card.

I built a circuit which seems to work, but I am getting some missed bytes, or sometimes added bytes.

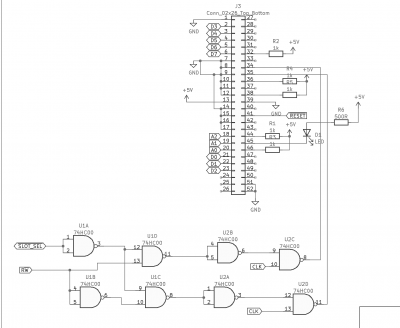

Here is a schematic of the circuit, but note I am using a CF to IDE adapter on my prototype board (to my understanding they are just passive adapters, am I wrong?)

Attachment:

cf-card.png [ 14.88 KiB | Viewed 1026 times ]

cf-card.png [ 14.88 KiB | Viewed 1026 times ]

Finally, here is the code snippet I use to read a sector from the card (adapted from

this code)

Code:

cf_wait:

wait_loop:

lda CF_ADDRESS + 7

and #$80

bne wait_loop

rts

cf_read:

phy

lda #<FAT_BUFFER

sta CF_BUF_PTR

lda #>FAT_BUFFER

sta CF_BUF_PTR + 1

ldy #0

loop:

jsr cf_wait

lda CF_ADDRESS + 7

and #$08

beq exit

lda CF_ADDRESS

sta (CF_BUF_PTR), y

iny

bne loop

inc CF_BUF_PTR + 1

bra loop

exit:

ply

rts

where FAT_BUFFER is a 512 byte buffer, CF_BUF_PTR is a ZP pointer and CF_ADDRESS is the base address of the CF card.

There is some more code which sets the LBA sector to read, please ask if seeing would be helpful.

And finally here is an example of what I am reading

Code:

EB 3C 90 42 53 44 20 20 34 2E 34 00 02 08 01 00 02 00 02 00 00 F8 F5 00 20 00 20 00 3F 00 00 00

A5 A7 07 00 80 00 29 EB 1A 4C 02 50 4C 41 4E 43 4B 36 35 30 32 20 46 41 54 31 36 20 20 20 FA 31

C0 8E D0 BC 00 7C 8E FB 8E D8 E8 00 00 5E 83 C6 19 BB 07 00 FC AC 84 C0 74 06 B4 0E CD 10 EB F5

30 E4 CD 16 CD 19 0D 0A 4E 6F 6E 2D 73 79 73 74 65 6D 20 64 69 73 6B 0D 0A 50 72 65 73 73 20 61

6E 79 20 6B 65 79 20 74 6F 20 72 65 62 6F 6F 74 0D 0A 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

And what I should be reading

Code:

EB 3C 90 42 53 44 20 20 34 2E 34 00 02 08 01 00 02 00 02 00 00 F8 F5 00 20 00 20 00 3F 00 00 00

A5 A7 07 00 80 00 29 EB 1A 4C 02 50 4C 41 4E 43 4B 36 35 30 32 20 46 41 54 31 36 20 20 20 FA 31

C0 8E D0 BC 00 7C FB 8E D8 E8 00 00 5E 83 C6 19 BB 07 00 FC AC 84 C0 74 06 B4 0E CD 10 EB F5 30

E4 CD 16 CD 19 0D 0A 4E 6F 6E 2D 73 79 73 74 65 6D 20 64 69 73 6B 0D 0A 50 72 65 73 73 20 61 6E

79 20 6B 65 79 20 74 6F 20 72 65 62 6F 6F 74 0D 0A 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 55 AA

As you can see, on line 3 for example I am reading

Code:

8E FB 8E

instead of

Code:

FB 8E

Can anybody see where I am going wrong? The card works perfectly when plugged in my laptop.

Thank you very much for any advice!

Edited to add:

My code seems to work fine, because I can reliably read the card information with ATA command $EC.

I does not seem to be a timing issue either because I get the same types of errors whether I run the computer at 1, 6 or 12 MHz...