I had an idea it might be fun to build something like a "souped-up BBC Micro" using a

65C816 processor instead of a 6502, running as fast as reasonably possible, and loads of RAM. As a stepping stone I built a prototype system to develop and test some building blocks. The prototype has a

65C816 running at 12.5MHz, 256KB RAM and a VGA display. The video controller accesses RAM on a multiplexed basis with the processor - when PHI2=0 the video controller accesses RAM, when PHI2=1 the processor accesses it. The video controller, RAM multiplexer and all address decoding is implemented in an EPM7128 CPLD which sits between the processor and RAM. The memory map implemented is as follows (only 20 address bits are used - the top 4 are ignored):

00000 - 3FFFF 256KB System RAM

1A800 - 3FFFF Frame buffer 150KB (640 x 480 x 4bpp)

40000 - 7FFFF Unused (possible extension RAM)

80000 - 8FFFF 64KB System ROM (Winbond W27C512)

90000 - BEFFF Unused

BF000 - BFFFF Writes to this area update HW scroll registers

C0000 - FEFFF Unused

FF000 - FFFFF 6522 VIA (even addresses only)

An FT240 USB module (this one:

https://www.ecstaticlyrics.com/electronics/USB/FT240X/ ) is currently attached to the VIA - this serves as keyboard input for now (PS2 support will be added later - that's one of the things which need developing). It also allows code to be downloaded to the board from a PC, and memory dumps to be uploaded to the PC. System output can be switched between the VGA display and the USB port.

An expansion connector is present. This is intended to be used to add an extra board with another CPLD on, which can be used to implement building blocks to be developed. These include a PS2 controller for keyboard connection, SPI controller to allow serial flash and/or SD/MMC to be used as mass storage, and I2C controller to connect to RTC and clock generator chip. The extra CPLD can also do address decoding for a second block of 256KB RAM - the Video PLD is completely maxed out on I/O lines, and very nearly maxed out on logic.

So, here's the schematic:

Attachment:

File comment: Schematic

816Proto_v0.1.pdf [252.67 KiB]

Downloaded 34 times

816Proto_v0.1.pdf [252.67 KiB]

Downloaded 34 times

Here are the Verilog files for the Video CPLD:

Attachment:

File comment: Verilog files for Video controller

VideoPLD.7z [4.62 KiB]

Downloaded 28 times

VideoPLD.7z [4.62 KiB]

Downloaded 28 times

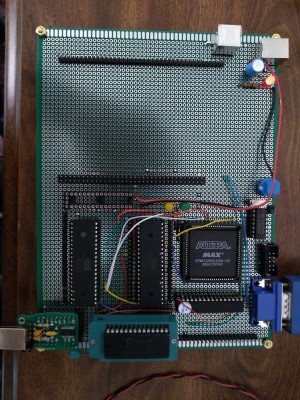

And here are some photos of the prototype.

This is the top of the board (component side):

Attachment:

File comment: Prototype board, component side

Board_Top.jpg [ 2.49 MiB | Viewed 1253 times ]

Board_Top.jpg [ 2.49 MiB | Viewed 1253 times ]

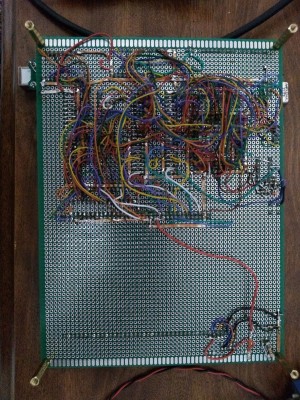

This is the mess of wires on the bottom (along with SMD caps and resistors)

Attachment:

File comment: Prototype board, wiring side

Board_Bottom.jpg [ 3.83 MiB | Viewed 1253 times ]

Board_Bottom.jpg [ 3.83 MiB | Viewed 1253 times ]

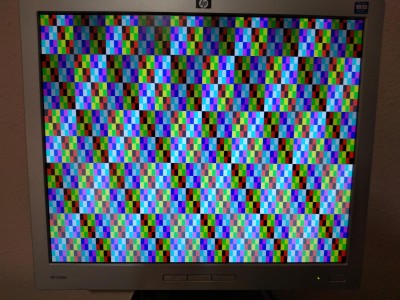

This is the test pattern the video controller displays before the processor starts running:

Attachment:

File comment: Video controller test pattern

VGA_Test_Pattern.jpg [ 1014.84 KiB | Viewed 1253 times ]

VGA_Test_Pattern.jpg [ 1014.84 KiB | Viewed 1253 times ]

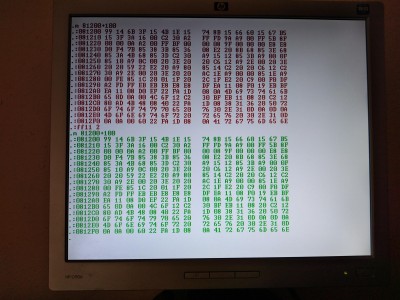

This is a memory dump from the system boot monitor on the video display:

Attachment:

File comment: Black & white text

Text_B&W.jpg [ 1.66 MiB | Viewed 1253 times ]

Text_B&W.jpg [ 1.66 MiB | Viewed 1253 times ]

Colour text:

Attachment:

File comment: Colour text

Text_Colour.jpg [ 1.39 MiB | Viewed 1253 times ]

Text_Colour.jpg [ 1.39 MiB | Viewed 1253 times ]