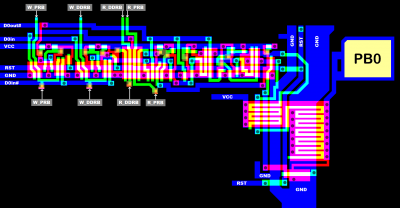

8) PB0 //PORT B

8 Bit I\O port, with push/pull outputs and _no_ pullup FET to VCC.

Layout for PB0..PB7 is similar, with some variations to make better use of chip space,

so we just focus on PB0.

;---

First for the output side:

DDRB0 (data direction register B) configurates,

whether PB0 works as an input (DDRB0=0)

or as an output (DDRB0=1).

It is cleared by RST during a hardware reset, defaulting PORT B to input.

DDRB0 is built around a gated RS flipflop.

High_active register write control signal W_DDRB clears/sets DDRBA0

according to the 6520 internal write data bus lines D0in and D0in#.

The high_active output of DDRB0 goes together with high_active register read control signal

R_DDRB into an "open collector" NAND gate, with the output connected to low_active

6520 internal read data bus line D0out#.

;...

The PRB0 (PORT B) data output register is built around another RS flipflop.

High_active register write control signal W_PRB clears/sets the PRB0 register

according to the 6520 internal write data bus lines D0in and D0in#.

The RS flipflop is cleared by RST during a hardware reset.

We have two NOR gates with push/pull output, controlling the FETs of the

PB0 output driver which are switching the PB0 pad either to GND or to VCC.

The high_active output of the DDRB0 register goes through an inverter, then into both NOR gates.

The low_active output of the PRB0 register goes into the NOR gate which drives

the FET switching PB0 to VCC.

The low_active output of the PRB0 register goes through an inverter,

then into the other NOR gate which drives the FET switching PB0 to GND.

;---

At the input side, the signal from the PRB0 pad goes through an inverter,

then into a 2:1 multiplexer built from a combination gate which

implements two AND gates feeding a NOR gate.

Means the output of the multiplexer is inverted.

It goes together with the high_active register read control signal R_PRB

into an "open collector" NAND gate, with the output connected to low_active

6520 internal read data bus line D0out#.

The other input of the 2:1 multiplexer is fed by the inverted output of the PRB0 register.

The multiplexer is controlled by DDRB0.

Means if PB0 works as an input, reading PRB gives the CPU what's on the PB0 pad.

If PB0 works as an output, reading PRB gives the CPU what's in the PRB0 register.

So when PB0 drives a large (capacitive) load when working as an output,

and it takes some time until the voltage at PB0 has reached the desired logic level,

the CPU still would be reading the correct/desired value from the PRB0 register.

And you won't have to worry when using read/modify/write instructions aiming for PRB.

But be aware:

If you have a glitch on PB0 when reading PRB0 in "input mode",

that glitch shows up on the 6502 data bus, too.

For better signal integrity, I would suggest to sample PB0 by a transparent latch

during PHI2=0 when building your own TTL or FPGA implementation of the 6520,

before sending it into the 2:1 multiplexer.

Attachment:

si6520_8_pb0.png [ 83.56 KiB | Viewed 376 times ]

si6520_8_pb0.png [ 83.56 KiB | Viewed 376 times ]

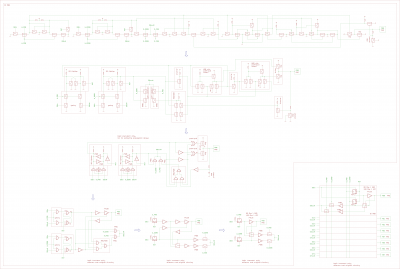

Attachment:

6520_8_pb0.png [ 224.4 KiB | Viewed 376 times ]

6520_8_pb0.png [ 224.4 KiB | Viewed 376 times ]