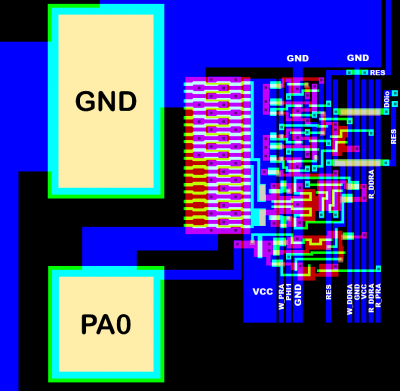

4a) PA0

Now for the parallel I\O ports, starting with PORT A.

In the silicon, PORT A, PA0..PA7 has push/pull output drivers,

but VCC of the individual drivers ist not connected to VCC of the chip.

So the PORT A output drivers only are able to switching the PA0..PA7 pads to GND.

Means for the "end user", PORT A has "open collector" outputs

with pullup resistors (FETs).

Note, that when a PORT A pin is configured as an output,

what you are getting when reading the PRA data register is

what's on the PA0..PA7 pads.

So you better be a bit paranoid/careful when using read/modify/write instructions

on the PRA register, like when driving a large capacitive load,

when an external source might be able to switch PA0..PA7 to GND,

or when trying to go for faster speed.

Layout for PA0..PA7 is pretty similar, so we just focus on PA0.

Registers and logic related to PA0 are attached to "the other end" of the PA0 pad driver.

PORT A register read/write control signals are generated in "6) address decoder".

;...

At the input side, the signal from the PA0 pad goes through an inverting super buffer,

then through an inverter, is sampled at PHI1 by a dynamic latch, then goes through

another inverter and into an "open collector" NAND gate with its output tied to the D0io bus.

The other input of the NAND is the high active R_PRA register control signal.

R_PRA enables the PRA data register read.

To make it short:

PA0 is sampled by a transparent latch at PHI1.

When the CPU reads the PORTA data register PRA with R_PRA,

if the output of the latch is LOW the D0io bus is pulled LOW.

For pullups on the D0io bus, see "13) internal data bus precharge".

;...

At the output side, first we have the PORTA data direction register Bit DDRA0.

The half_static DDRA0 register Bit is written with the high_active W_DDRA signal at PHI2,

it is refreshed during PHI1, and when RES is active it is cleared at PHI1.

For reading DDRA0 from the CPU:

Basically, the inverted output of the DDRA0 register goes into an

"open collector" NAND gate with its output tied to the D0io bus.

The other input of the NAND is the high active R_DDRA register control signal.

R_DDRA enables the DDRA read at PHI2.

To prevent glitches (during PHI2 register write), the output of the DDRA0 register Bit

is sampled by a transparent latch at PHI1 before it goes into two NAND gates.

The output of each NAND gate goes through an inverter.

The outputs of the inverters are controlling the driver FETs which are switching PA0 to GND (or not to VCC).

When DDRA0 is 0, PA0 acts as an input because said driver FETs are disabled.

When DDRA0 is 1, PA0 acts as an output, and the driver FETs are switching PA0 either to GND (or not to VCC).

//The driver FETs which are supposed to switching to VCC are not connected to VCC, that's why "(or not to VCC)".

//In the 8520, PA0..PA7 drivers are push/pull drivers, switching to VCC indeed.

Also, we have the PRA0 data output register Bit.

The half_static PRA0 register Bit is written with the high_active W_PRA signal at PHI2,

it is refreshed during PHI1, and when RES is active it is cleared at PHI1.

The output of the PRA0 data output register Bit is sampled by a transparent latch at PHI1

to prevent glitches (during PHI2 register writes), then goes through two inverters

which control the two NAND gates, for making the output driver FETs switching PA0

either to GND when data output register Bit PRA0 = 0,

(or not to VCC when data output register Bit PRA0 = 1.)

;...

Attachment:

si8521r1_4a_pa0.png [ 77.16 KiB | Viewed 2598 times ]

si8521r1_4a_pa0.png [ 77.16 KiB | Viewed 2598 times ]

Attachment:

8521r1_4a_pa0.png [ 102.26 KiB | Viewed 1828 times ]

8521r1_4a_pa0.png [ 102.26 KiB | Viewed 1828 times ]