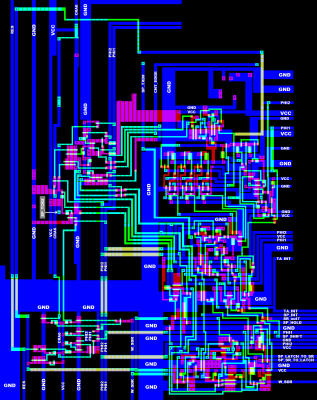

11b) serial port control

The only thing that 8522 and 8521 have in common is DIP40.

And that the control circuitry for the serial port

uses a ring counter with an edge detector attached

for checking if a serial transfer is completed.

In 'transmit' mode, the shift clock for the serial data transmission

is generated inside the chip, toggles with 16 Bit timer A underflows,

canges at PHI1, and comes out of the CNT pad.

In 'receive' mode, the shift clock for the serial data transmission

has to be generated from outside the chip, and fed into the CNT pad.

;...

CRA6 control register A Bit selects the mode for the serial port:

0 = shift in //receive, RX

1= shift out //transmit, TX

First, we have an edge detector scanning for a rising/falling edge at CRA6.

If CRA6 changes, the serial port control logic is reset for one PHI2 cycle.

Means, that switching the serial port mode from 'receive' to 'transmit',

or from 'transmit' to 'receive', serial port control logic is initialized again

in the whole PHI2 cycle that follows the CRA register write cycle.

Also, an active RES signal resets the serial port control logic.

The high_active reset signal SP_RES (generated by CRA6 edge detector output OR RES)

affects the following of the serial port control logic:

'TX_initiate' RS flipflop is cleared,

'TX_active' RS flipflop is cleared,

Toggle counter which generates SP_TCK is set, //default: serial transmit clock is HIGH

Bit counter is cleared. //4 Bit ring counter counting the received/transmitted Bits

;...

If the serial port data latch was written in the previous PHI2 cycle

with high_active register control signal W_SDR, and if CRA6 = 1 (transmit mode),

the 'TX_initiate' RS flipflop is set at PHI1.

;

Said RS flipflop (built from two NOR gates) has the purpose of transferring

the contents of the data latch by high_active control signal SP_LATCH_TO SR

into the shift register (at PHI1)...

when no active transmit shift sequence already is running.

The RS flipflop is cleared when the transfer is done.

When the transfer is done, this sets the 'TX_active' RS flipflop

(built from two NOR gates), which enables toggling of the serial port transmit clock.

Said flipflop is cleared with the high_active SP_INT signal

which indicates the end of a shift sequence...

when the 'TX_initiate' RS flipflop indicates that a new sequence is not needed.

A one Bit binary counter (forced to 1 by SP_RES) basically generates

the serial port transmit clock SP_TCK.

The counter flips in the PHI2 cycle after TA_INT was active

(after a 16 Bit timer A underflow, that is).

If no transmit sequence is running and SP_TCK is LOW,

the next TA_INT makes SP_TCK flip to HIGH again.

//Default for SP_TCK is HIGH.

Basically at the falling SP_TCK edge, the output of an edge detector

advances the Bit counter and makes the shift register shift with

high active control signal SP_SHIFT by one step (at PHI1).

If the shift register does not shift,

and if the data latch is not transferred into the shift register,

high_active control signal SP_HOLD refreshes the contents

of the shift register Bits (at PHI1).

The Bit counter (which counts the Bits in a shift sequence)

is a 4 Bit ring counter, and it's quite difficult to spot the MSB

of the counter as such in the silicon.

;

The output of the rising edge detector which basically scans SP_TCK

goes into a RS flipflop, which generates two clock signals

(which change at PHI2 in the next PHI2 cycle) for the counter:

If there was a rising edge, the next counting step is prepared.

If there was no rising edge, the outputs of the counter Bit cells are changed.

A NOR gate (fed from a delay chain built from transparent PHI1\PHI2 latches)

makes sure that refresh for the half_static latches in the Bit counter

is not done before the counter cell Bit outputs are updated.

//Output of the NOR changes at PHI1.

//16 Bit timer A at 1MHz could give you baud rates down to 7.629... Hz,

//so mere dynamic latches won't do for building the ring counter.

The 4 outputs of the ring counter go into a NOR gate plus an edge detector.

After the ring counter has reached the value $0, SP_INT goes active

for one PHI2 cycle (at PHI1), indicating the end of a shift sequence.

SP_INT goes into "10a) ICR". //interrupt control register

;...

High_active signal CNT_EDGE is generated in "12) CNT edge detector".

It is active for one PHI2 cycle after a rising edge on the CNT pad was detected.

It changes at PHI1.

In 'receive mode', it is used for advancing the Bit counter and the shift register.

//At the rising edge of CNT.

There is no difference between 'transmit' and 'receive' mode when it comes to

how the ring counter works and how the SP_INT signal is generated.

Anyhow, in 'receive' mode SP_INT triggers the high_active control signal

SP_SR_TO_LATCH, which transfers the contents of the shift register

into the data latch (at PHI2).

;...

Attachment:

si8521r1_11b_sp_control.png [ 270.32 KiB | Viewed 1619 times ]

si8521r1_11b_sp_control.png [ 270.32 KiB | Viewed 1619 times ]

Attachment:

8521r1_11b_sp_control.png [ 411.98 KiB | Viewed 1619 times ]

8521r1_11b_sp_control.png [ 411.98 KiB | Viewed 1619 times ]