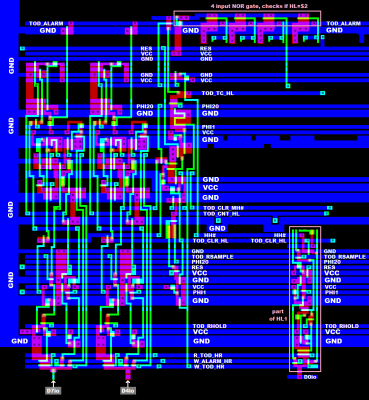

14f) HH, TOD

In the 8521, TOD is a

12-hour clock.

//in the 8520, there is no HH, TOD in the silicon.

//a.m. (from Latin ante meridiem, translating to "before midday")

//p.m. (from Latin post meridiem, translating to "after midday").

We have two one_Bit counter cells, labelled HH and PM (both of them have identical layout),

which are just a variation from the one_Bit counter cells

we had for generating the shift register clock in "11) SP control"

and for generating the PB6,PB7 square wave signal in "8e) 9e) timer control logic".

;

A rising edge on the toggle signal flips the Bit.

HH is the MSB of the hour counter. //Hour counter is HL1,HL2,HL4,HL8,HH.

PM is the AM\PM flag. //also a one_Bit counter.

When HL counter has to be incremented (because the MH counter output carry is active)

and HL counter already is $9 while HH=0, HL is cleared to $0 and HH is set to 1.

When HL counter has to be incremented (because the MH counter output carry is active)

and HL counter already is $2 while HH=1 (when hours = decimal 12), HL is set to $1 and HH is cleared.

When the hour counter reaches 12, PM toggles.

Note, that the ML output carry doesn't go into the equation,

so writing decimal 12 into the hours if the hours already were not 12 this will toggle PM.

//And please take a look at wikipedia

Confusion at noon and midnight.

Also, we have the ALARM registers ALARM_HH and ALARM_PM,

and the related comparators.

;

Chip layout of that part is different from the ALARM registers

and comparators we had in the rest of the BCD counters,

but at logic design level the transistor level schematics are identical.

So far for the simple version.

;...

PM flag:

We have sort of a comparator which checks if HH=1 and if HL=$2.

The rising edge of the comparator output toggles the PM flag.

Again, note that the MH output carry doesn't go into this.

The PM flag toggles when TOD reaches 12:00:00, that yes.

But a side effect is that when writing "HH=1 and HL=$2" to the TOD_HR register,

and the TOD_HR register previously was not "HH=1 and HL=$2", this toggles the PM flag.

In this case, you would have to write with the PM Bit _inverted_ into the TOD_HR register

to compensate for this.

;...

HL1 Bit and HH#:

TOD jumps from 12:59:59 to 01:00:00.

For implementing this, the designers had pulled a trick.

If there was an overflow in the MH counter,

and either HH=0 AND HL=$9, or HH=1 AND HL=$2,

the high_active control signal TOD_CLR_ML

clears the Bits HL8,HL4,HL2 and loads HL1 with HH#.

But wait a minute:

Wouldn't this make TOD jump from 09:59:59 to 11:00:00 and from 12:59:59 to 00:00:00 ?

After checking that water still flows from out of the water tap down into the basin,

and that a screwdriver still falls toward the mass center of planet Earth when getting dropped,

I felt a need to take a closer look at why the designers had used HH# instead of HH.

The trick is hidden within the timing.

The HL+HH overflow is sampled by a transparent latch at PHI20

(which is high at PHI2 in every fourth PHI2 clock cycle)

for generating the TOD_CLR_HL signal which loads HH# into HL1.

TOD_CLR_HL is sampled by another transparent latch at PHI1,

for generating the TOGGLE_HH signal.

A rising edge on TOGGLE_HH signal flips the HH counter Bit.

So TOD_CLR_HL changes half a PHI2 cycle _before_ TOGGLE_HH changes.

This means, that for 0.5 PHI2 cycles, the wrong HH value is written into HL1,

and for 3.5 PHI2 cycles (after HH has toggled) the _correct_ HH value is written into HL1.

But you won't notice from the state of the HL1 Bit (except for a 0.5 PHI2 cycle delay).

//A nice trick for saving some logic gates.

And that's why TOD indeed jumps from 09:59:59 to 10:00:00 and from 12:59:59 to 01:00:00,

I had checked this on a real C64 by resorting to peek() and poke() just to be on the safe side...

;...

Attachment:

si8521r1_14f_tod_hh_pm.png [ 77.13 KiB | Viewed 1843 times ]

si8521r1_14f_tod_hh_pm.png [ 77.13 KiB | Viewed 1843 times ]

Attachment:

8521r1_14f_tod_hh_pm.png [ 232.1 KiB | Viewed 1843 times ]

8521r1_14f_tod_hh_pm.png [ 232.1 KiB | Viewed 1843 times ]