I'm using W65C22

N (yes, NMOS-compatible version), I bought it from Mouser, so it must be a modern part.

(My 6551 is also W65C51

N - I preferred them over CMOS versions because of open-drain /IRQ that can be wire OR'ed, and also because I want them to be compatible with some of my other NMOS chips that I might be adding to my SBC).

I'm reading PS/2 in a bit-banging fashion through 65C22N:

- PS/2 data -> PB4

- PS/2 clock -> CB2

I have my VIA fire an interrupt on the falling edge of CB2:

Code:

lda #%01111111 ; Disable all interrupts

sta VIA1_IER

lda #%10001000 ; Set interrupt flag for CB2 (page 27)

sta VIA1_IER

My ISR then counts 11 bits and registers a "key pressed/released" flag.

However I'm sometimes getting weird /IRQ assertions when pressing keys on a keyboard (happens <1% of time, but is annoying as hell):

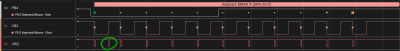

Attachment:

phantom_irq.png [ 23.4 KiB | Viewed 875 times ]

phantom_irq.png [ 23.4 KiB | Viewed 875 times ]

The green circle shows a place where /IRQ is asserted despite CB2 is rising. You can clearly see that it's aligned with CB2. This results in clock skew, so now all my PS/2 packets are off by 1 bit. This happens in random places.

- My /IRQ is pulled up with 5K resistor. Same issue is reproducible with my another SBC which has a 3.3K pull-up.

- Both PS/2 lines are pulled up with 1K resistors.

- No other hardware is using /IRQ - it's wired only from 65C22N to 65C02S (I've removed 65C51N for debugging.)

- My ISR takes ~4us to clear VIA's interrupt flag (I'm doing that as early as possible) and you can clearly see that the /IRQ line is released normally.

- This seems to occur much more frequently when I rapidly slam my keyboard. However, my logic analyzer still properly decodes PS/2 packets.

- I'm running @ 8 MHz.

Why could this be happening?

EDIT: This is also reproducible with another keyboard AND with another revision of my SBC (which has totally different PCB traces, so I highly doubt that crosstalk is involved.)

<s>EDIT 2: I'm going to try another VIA for this. That's the only part I've reused in both builds. I highly doubt that it's my software that's guilty - the code is very simple.</s> nope - same issue with a different W65C22N.

EDIT 3: Could it be due to mixing W65C02S & W65C22N?

EDIT 4: I think I should replace my 'N chips with 'C versions and join IRQ lines through 74HC08 (or 74HC11 to have an extra line for open-drain chips.)

_________________

/Andrew

deck65 - 6502 slab with screen and keyboard |

ПК-88 - SBC based on KM1810VM88 (Ukrainian i8088 clone) |

leo80 - simple Z80 SBC

nice65 - 6502 assembly linter |

My parts, footprints & 3D models for KiCad/FreeCAD