Hi all,

I've been refining my

65C816 circuitry for over a year in my YouTube series, and I'm at a point where I consider the design stable enough to make a PCB. This project aims to provide in a single board everything needed to kick off a new

65C816 project. It includes a clock and reset circuit, and then everything that should have been part of the main processor, in my opinion. Here is a list of features and design constraints:

- Built to plug in a breadboard with a 58-wide pin header at the bottom of the board

- Assuming a 150ns EEPROM and a fast address decode circuit, it is specified to run at 4MHz worst case, over temperature. I suspect significant overclocking can be achieved.

- Uses only discrete, through-hole, and in-production components (with an exception for the obsolete DIP format DS1035M-10, which can be replaced by an in-production SMD format DS1135Z-10, depending on your preference)

- Includes a 4MHz clock source that can be disabled and replaced by an external source

- Includes a power-up reset circuit with a manual reset button

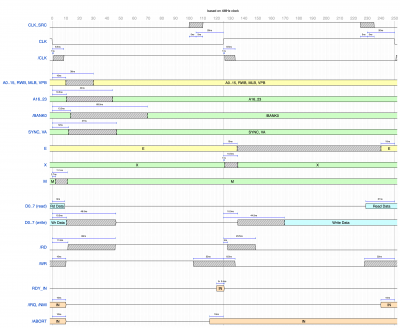

- Uses out-of-phase internal clocks to generate read and write pulses and control the data bus demultiplexing, all in accordance with proper timing (read hold time >= 10ns, write pulse time <= 10ns, bank address latch time <= 10ns but hold time >= 10ns)

- 74AHC logic used for gentle edges on the breadboard while keeping fast propagation. Faster edges (74AC, DS1035) have optional source termination.

- on top of the CPU signals are provided both positive and negative reset and clock signals, /RD and /WR pulses, VA and SYNC signals, Bank0 signal for simple memory maps

- Data bus is free when the clock is low for video access interleaving

- the RDY pin is split into an input-only RDY_IN, and output-only /WAI. RDY_IN is registered on the rising edge of the clock to ensure internal consistency

- the MX pin is split into M and X

- using Bus Enable for DMA is fully supported, with the data and address buses, R/W, /RD, /WR, and VA signals being tri-stated by BE. They all have weak pull-ups/downs for default values while experimenting with BE on the breadboard.

- using RDY_IN to pause execution as if the clock were held high is fully supported for both reads and writes, with /RD and /WR being kept low and the bank address latch staying closed.

Being in spec with timings and supporting everything means the design is a bit more complicated than what you might need in your project. Presumably, you only need to build this board once to be able to re-use it in most cases. Except for anything faster than 4MHz I guess. Speed, Feature Completeness, Discrete 5V DIP ICs, choose two

I suspect a future revision with a CPLD will be able to achieve more speed while keeping the features.

I would love to hear your feedback on this design, as I will be routing the PCB soon. Is there anything I missed or might want to tweak? Attached is the schematic as well as the timing diagrams.

I plan on releasing the final board as open-source, and also (maybe? full-disclosure) to sell complete kits on Tindie.

Attachment:

breakout.pdf [212.81 KiB]

Downloaded 61 times

breakout.pdf [212.81 KiB]

Downloaded 61 times

Attachment:

breakout-bw.pdf [209.57 KiB]

Downloaded 48 times

breakout-bw.pdf [209.57 KiB]

Downloaded 48 times

Attachment:

Timing Main.png [ 256.7 KiB | Viewed 1137 times ]

Timing Main.png [ 256.7 KiB | Viewed 1137 times ]

Attachment:

Timing BE.png [ 1.05 MiB | Viewed 1137 times ]

Timing BE.png [ 1.05 MiB | Viewed 1137 times ]