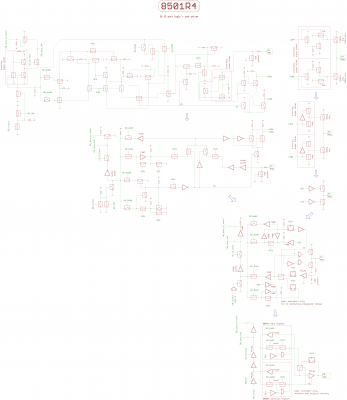

9) IO port.

The IO port logic is rather compact, and west from the P1..P3 pad drivers.

From North to South, we have the logic related to P0, P1, P2, P3, P4, P6, P7,

then the logic which makes the data Bit and data direction Bit for P5 zero during reads.

//There is no P5 IO port in the 8501.

//North from the IO port logic blocks we have data read/write control.

//South from the IO port logic blocks we have the IO address decoder.

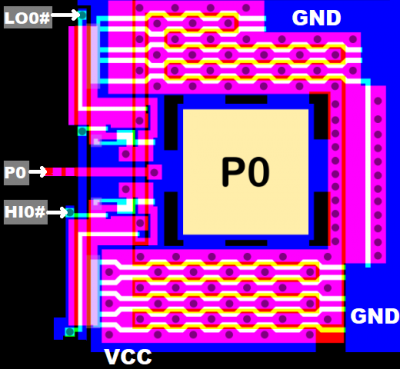

P0 pad driver layout is a bit different from P1 pad driver layout, but the circuitry is identical.

The P0 pad driver is nothing fancy.

Attachment:

si8501_9_io_port_driver.png [ 49.41 KiB | Viewed 2805 times ]

si8501_9_io_port_driver.png [ 49.41 KiB | Viewed 2805 times ]

Note, that the ESD protection FET is not located close to the P0 pad.

It's part of the P0 IO port logic block, which isn't optimal.

My guess is that the designers did run out of space on the chips,

and that unlike with the 6522 and 6526 the IO port pins of the 8501

were not ment to give signals to the outerworld (outside of the computer).

Looks like the IO port logic blocks were created by copy+paste,

means the layout of all the IO logic blocks is more or less the same.

So we only take a look at the P0 IO port logic.

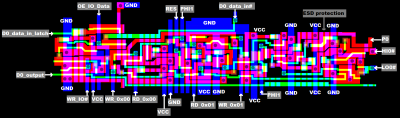

The low_active WR_IO# control signal puts the D0_output of the CPU on the IO data bus during peripheral writes.

An inverting super buffer with a FET switch at the output controlled by the high_active OE_IO_Data signal

puts the inverted data from the IO data bus on D0_data_in#.

D0_data_in# also is fed by the D0 pad input buffer.

D0_data_in# goes through a simple inverter before it enters the CPU as D0_data_in_latch.

In the IO logic, we have two latches:

WR_0x00 writes the P0 data direction latch.

WR_0x01 writes the P0 data latch.

The P0 input is sampled at PHI1 by a latch.

Depending on if P0 is configurated as an input or an output,

we have a multiplexer that either sends the output of the P0 latch to the IO data bus,

or the output of the P0 data register.

Connections at the multiplexer look a bit unusual,

but I would say if a designer is paranoid about output pins of different chips working against each other,

it seems to make sense.

Attachment:

si8501_9_io_port_logic.png [ 70.65 KiB | Viewed 2805 times ]

si8501_9_io_port_logic.png [ 70.65 KiB | Viewed 2805 times ]

Attachment:

8501_9_io_port.png [ 191.48 KiB | Viewed 2805 times ]

8501_9_io_port.png [ 191.48 KiB | Viewed 2805 times ]

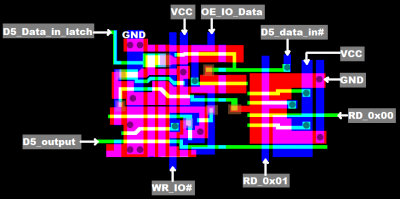

8501 has no P5.

There is a block circuitry that forces the P5 data Bit and data direction bit to 0,

and it looks like a normal IO block just was cut down to the bare minimum.

Attachment:

si8501_9a_unused_p5.png [ 25.08 KiB | Viewed 2805 times ]

si8501_9a_unused_p5.png [ 25.08 KiB | Viewed 2805 times ]

Attachment:

8501_9a_unused_p5.png [ 44.77 KiB | Viewed 2805 times ]

8501_9a_unused_p5.png [ 44.77 KiB | Viewed 2805 times ]