Ok, I need to be more diligent about posting updates here as I publish my videos, I'm two episodes behind.

In

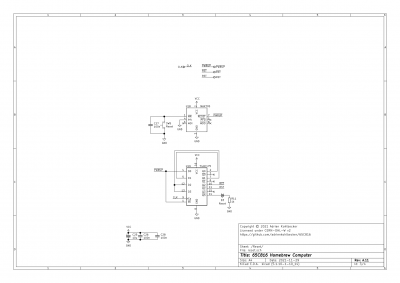

Episode 10 - Power-up Reset I build a power-up circuit using a MAX705. Even though I used a DS1813 in my 6502 build, I like the MAX705 here for its watchdog, and separate manual reset input.

I also had to make sure that reset pulses would be registered by the CPU even if I'm running with a slow or manual clock. For that I chained the reset through 3 flip flops, to ensure it stays low for at least 2 full clock cycles.

Here is the final reset circuit:

Attachment:

reset-Reset.png [ 175.74 KiB | Viewed 935 times ]

reset-Reset.png [ 175.74 KiB | Viewed 935 times ]

Next, in

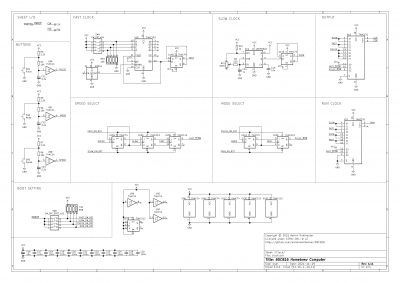

Episode 11 - Clock Module #3, I went back to the clock circuit and added glitch-free clock switching. By relying on the property that my clocks have vastly different frequencies, I'm able to ensure I always switch when a low-cycle of the destination clock begins and overlaps with a low cycle of the active clock. For that, I used a chain of negative edge triggered JK flip flops. I also had to change my output stage to a 74HC151 multiplexer, which is nice because it keeps the inverted output I had on the 74HC74

I also added a dip switch to select which clock mode and speed the circuit boots in on power up, so I can change it based on what I'm doing (hardware, software...)

Here is the current clock circuit

Attachment:

clock-Clock.png [ 430.41 KiB | Viewed 935 times ]

clock-Clock.png [ 430.41 KiB | Viewed 935 times ]

Next episode will be about starting up the CPU (finally, yay!) using a NOP generator.