After cbmeeks posted the link to my new 65C816 computer YouTube series and seeing the interest that forum members had, I thought it would be a good idea to create a project thread to exchange ideas.

Here is the link to the playlist where you can watch it from the beginning:

The goal of the project is to build a 65C816 development platform and learn about the CPU. I'm not going for ludicrous speed and features for revision A, here are the goals:

- Runs at 4Mhz

- Prototyped on a breadboard, through-hole ICs only, no programmable logic

- 32KB RAM, 32KB ROM, 512KB extended RAM

- 65C22 and 65C21 for peripheral I/O

- 65C51 for UART

Conceptually, it will be similar to WDC's own development board. I know the 65C51 has a bug but it seems like a good period-accurate starter, and I'll explore newer PLCC options in revision B.

The goal of the series is to provide a good description of all the design decisions, including going in-depth on timing, and be a more advanced complement to something like Ben Eater's 6502 series, as well as show more love to this cool CPU, that it currently lacks.

You can find the source (hardware, software, and documentation) for this project on my GitHub here: https://github.com/adrienkohlbecker/65C816

Once this first revision is complete, I'm thinking of using it to explore designs going in a few directions:

- Moving to surface mount, maybe even to 3.3V

- Programmable logic

- Video and keyboard I/O (could be TMS9918+PS/2?)

- Running at 14Mhz

- And a bunch more ideas floating in my head... probably won't have the time to do them all

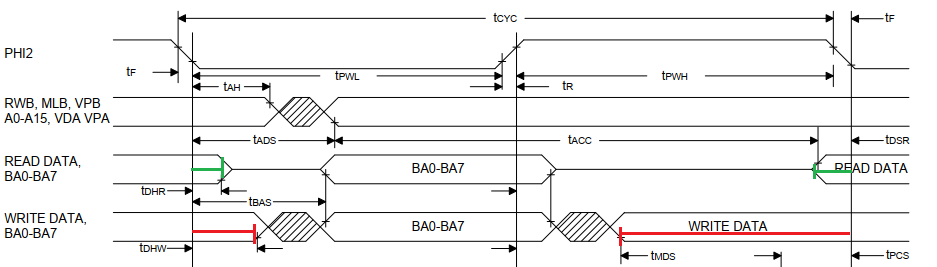

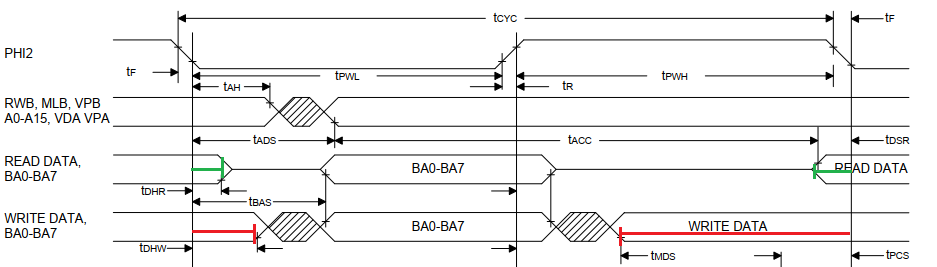

At this point in time, I'm exploring the Data Bus / Bank Address demultiplexing circuit, and improving the one shown in the datasheet by making it work in more situations (using BE, RDY). The next steps are to build a clock and reset circuit, and add memory.

I hope you enjoy this project and that this thread will spark some interesting conversations!