If I understand you correctly, you'd do this:

This assumes the VIC-II can handle a cycle width half as wide as it normally sees, but for sake of argument...

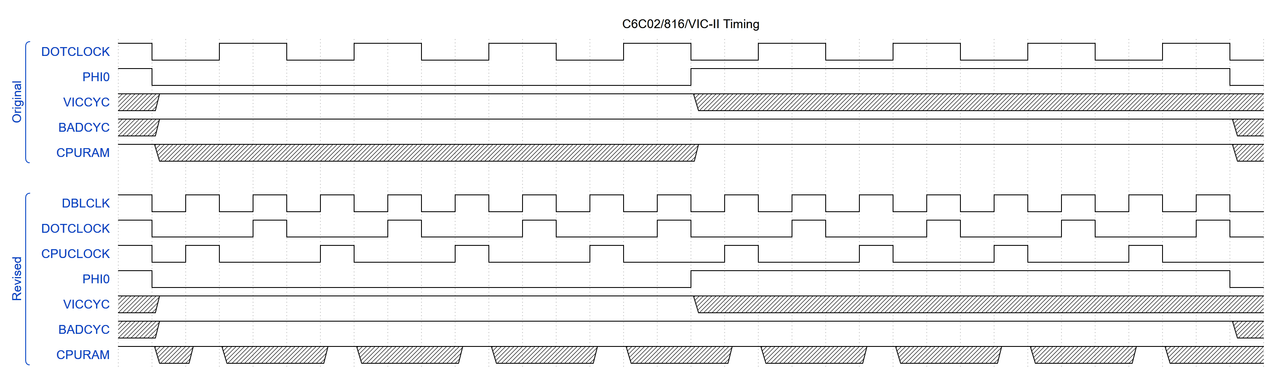

As you can see, PHI0 is still 1MHz, and a bad cycle still consumes 100% of it, meaning the entire cycle is not available for the CPU.

(For reference, this timing diagram is from WaveDrom -

https://wavedrom.com/editor.html and the code to create it is:

Code:

{signal: [

["Original",

{name: 'DOTCLOCK',wave: 'hl.h.l.h.l.h.l.h.l.h.l.h.l.h.l.h.l'},

{name: 'PHI0', wave: 'hl...............h...............l'},

{name: 'VICCYC', wave: 'x1...............x................'},

{name: 'BADCYC', wave: 'x1...............................x'},

{name: 'CPURAM', wave: 'hx...............1...............x'},

],

{},

["Revised",

{name: 'DBLCLK', wave: 'hlhlhlhlhlhlhlhlhlhlhlhlhlhlhlhlhl'},

{name: 'DOTCLOCK',wave: 'hl..hl..hl..hl..hl..hl..hl..hl..hl'},

{name: 'CPUCLOCK',wave: 'hlhl..hl..hl..hl..hl..hl..hl..hl..'},

{name: 'PHI0', wave: 'hl...............h...............l'},

{name: 'VICCYC', wave: 'x1...............x................'},

{name: 'BADCYC', wave: 'x1...............................x'},

{name: 'CPURAM', wave: '1x1x..1x..1x..1x..1x..1x..1x..1x..'},

]

],

config: { hscale: 1 },

head: { text:'C6C02/816/VIC-II Timing' },

}

An alternative would be to send 8 double speed clocks to the VIC, and then 8 periods of no clock, and let the CPU use that second set of 8 clocks to do work, but I doubt VIC would operate with such an irregular clock, so I think that is a non starter.

The best bet is to throw each address/data line set into a mux with some really fast RAM (if you're planning to run the 65C02 at 8MHz, that means RAM needs to be <125nS, but you need to access it only on the high half cycle, so 62nS or better) and a latch. In the front half of each half cycle, you allow VIC to access, latching the data into a register and then presenting it to the VIC as DATA for the remainder of that half cycle. On the back half of the cycle, let the CPU have the RAM directly. Most of the VIC accesses would go unused, but each device would have total access to RAM (some provision needs to be made for when the CPU needs to talk to the VIC, but to do that, it needs to slow down to 1MHz, and then you're waiting on the VIC anyway:

Code:

{signal: [

["Revised",

{name: 'DBLCLK', wave: 'hlhlhlhlhlhlhlhlhlhlhlhlhlhlhlhlhl'},

{name: 'DOTCLOCK',wave: 'hl.h.l.h.l.h.l.h.l.h.l.h.l.h.l.h.l'},

{name: 'CPUCLOCK',wave: 'hl.h.l.h.l.h.l.h.l.h.l.h.l.h.l.h.l'},

{name: 'PHI0', wave: 'hl...............h...............l'},

{name: 'RAMCLOCK',wave: 'hl.h.l.h.l.h.l.h.l.h.l.h.l.h.l.h.l'},

{name: 'VICRAM', wave: 'x1.x.............1.x..............'},

{name: 'CPURAM', wave: '1x.1.x.1.x.1.x.1.x.1.x.1.x.1.x.1.x'},

]

],

config: { hscale: 1 },

head: { text:'C6C02/816/VIC-II Timing #2' },

}

Realistically, the VIC address lines won't settle down that fast, so you'd need to put the VIC data access about midway through the 1MHz half cycle (but, I didn't feel like updating my diagram, so just imagine it). In any case, that's the best way to use a 1MHz VIC-II and an 8MHz '02/816 and not have to deal with bad cycles.

Jim