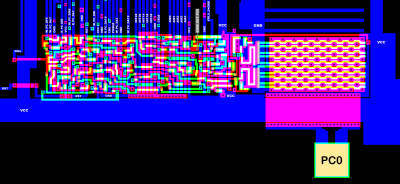

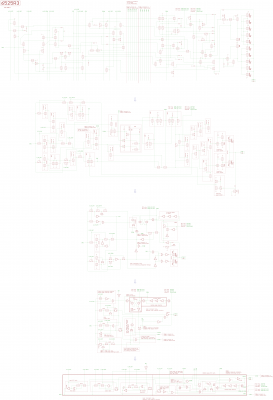

11) PC0..4

To me, it feels like the designers had taken the layout from "10) PA0",

cut it into two parts, and crammed some ciruitry in between...

which is related to edge detection and sensing the interrupt inputs.

Layout for PC0..4 is pretty identical, so I'll focus on PC0.

In mode 0, Port C behaves pretty much like Port A and Port B.

In mode 1, things are very different, and PC0..4 are the interrupt signal inputs I0..4.

Now for the differences, and I'm only describing the concept:

;---

We have a falling edge detector, which makes use of gate delays for sensing a falling edge.

Between the input of the edge detector and the PC0 pin,

we have an XOR gate to change the polarity of the signal PC0 for making it possible

to sense for rising/falling edge:

by sending a signal I had named POL0 into the other input of the XOR gate.

Note, that using an XOR here in this way is the "cheap" way for implementing rising/falling edge detection:

If PA0 is high and POL0 changes from low to high, the output of the XOR goes low and triggers the edge detector.

If PA0 is low and POL0 changes from high to low, the output of the XOR goes low and triggers the edge detector.

So when changing the polarity it would be a good idea to first disable the interrupt related to PA0 before changing POL0,

then to change polarity, then to clear the related interrupt flag after the change, then to enable the interrupt again.

Hypothetically spoken, because POL0..POL2 for PC0..PC2 are directly connected to GND, so PC0..PC2 only can sense falling edge,

but POL3 and POL4 are fed by the IE3 and IE4 Bits from the Control Register.

The XOR gates for PC0..PC2 are somewhat redundant, nevertheless they are present in the silicon.

In mode 1, the edge detectors emit a high pulse when detecting a falling edge.

In mode 0, the edge detectors are disabled.

Note, that the output of the PC3 edge detector EDGE_DET_PC3 is buffered and goes

as EDGE DET_PC30 to "8) CA, Port A handshake logic".

Also, the output of the PC4 edge detector EDGE_DET_PC4 is buffered and goes

as EDGE_DET_PC40 to "9) CB, Port B handshake logic".

;---

But back on topic.

We have a RS flipflop built from two NOR gates, which is the 'INT0 interrupt latch'.

a) It is set by the edge detector.

b) It is cleared in mode 0.

c) It is cleared, after writing a 0 to the Port C data write register.

d) It is cleared during a PUSH when the interupt logic had acknowledged INT0 by the AIR0 signal.

The way how the flipflop is built causes 'set' to have a higher priority than 'clear'.

The state of the INT0..4 interrupt latches can be sensed by reading the Port C data register.

Some more details:

c)

When the Port C data write register is written by the control signal W_PC_DAT

with data from the D0io data bus line, D0io also is written into a dynamic transparent latch.

An edge detector senses the falling edge of W_PC_DAT, emitting a high pulse on W_PC_DFE after the write

which goes into an AND gate, together with the inverted output of the dynamic latch.

The output of said AND gate clears the output of the INT0 interrupt latch.

d)

If the state of the AIR0 signal is different from the output of the INT0 interrupt latch,

and the low_active PUSH# signal goes active, the INT0 interrupt latch is cleared.

;---

The Port C direction register is used for masking/enabling the interrupts:

A NAND gate is fed with the output of the INT0 interrupt latch,

plus with Bit 0 from the Port C direction register.

If Bit 0 of the Port C direction register is set,

and the output of the INT0 interrupt latch is active,

the NAND gate gives out low on INT0# (low_active),

which then goes to the interrupt logic.

//similar game for PC1..4, INT1..4#, and AIR1..4.

Note the creative/confusing wiring in the schematic:

the designers had pulled a trick for saving some chip space:

The input of the NAND gate which generates INT0#

and the input of the XOR gate which compares the output of the INT0 interrupt latch to AIR0

are not wired to the output of the INT0 interrupt latch (as you would have expected),

but to the input of the PC0 data read latch

(in mode 1, a 2:1 multiplexer feeds said input from the INT0 interrupt latch).

;---

The output section of PC0..4 is a bit different from what we had in "10) PA0",

because in mode 1 the output drivers for PC0..4 are disabled,

that's _why_ the Port C direction register can be used for masking/enabling interrupts instead.

Attachment:

si6525_11_pc0.png [ 128.82 KiB | Viewed 1007 times ]

si6525_11_pc0.png [ 128.82 KiB | Viewed 1007 times ]

Attachment:

6525_11_pc0.png [ 383.03 KiB | Viewed 1007 times ]

6525_11_pc0.png [ 383.03 KiB | Viewed 1007 times ]