Thank you, all, for the replies. The topic has drifted somewhat, which is partly my own fault due to lack of proper emphasis in the lead post.

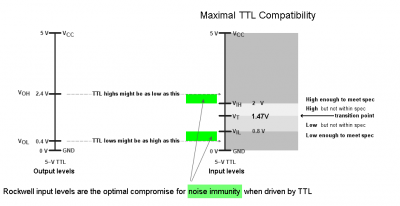

The term "TTL compatible" appears occasionally on this forum, and readers (especially newbies) may gather that it has a single, unambiguous meaning. But there are two tiers of "TTL compatibility," and they differ markedly.

That is my key point -- two tiers. We have what I would call genuine TTL compatibility, which any engineer would prefer due to its maximal noise immunity. The second tier is what I'd call "hope it works" TTL compatibility -- and very often it

does work (as I was careful to mention in the lead post, and others have echoed that).

But let's not confuse the two tiers:

Attachment:

TTL output to Rockwell CPU .png [ 23.15 KiB | Viewed 8405 times ]

TTL output to Rockwell CPU .png [ 23.15 KiB | Viewed 8405 times ]

Attachment:

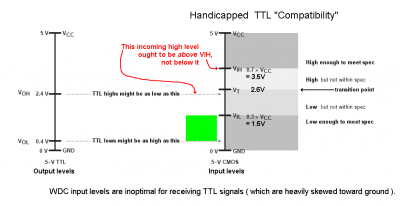

File comment: handicapped TTL compatibility

TTL output to WDC CPU .png [ 23.64 KiB | Viewed 8405 times ]

TTL output to WDC CPU .png [ 23.64 KiB | Viewed 8405 times ]

There are also two tiers when we say a certain combination "will work." We need to remember that the TTL-to-WDC combination is far more prone to

stop working in noisy circumstances. Those include proximity to external noise, of course, but other important factors include supply noise, crosstalk and inoptimal construction techniques.

The lower of the two attached diagrams shows that the TTL-to-WDC combination actually has

negative noise immunity when conveying a 2.4V logic high. Luckily, the shortfall is small when comparing 2.4V with the input transition point, VT. Especially without DC loading, the VOH of most TTL-output devices

is likely to exceed the TTL spec of 2.4V... at least sufficiently to bring it slightly above the transition point, and this explains why success is often reported.

But operating near the transition point involves tradeoffs. Poorer noise immunity is the obvious factor, but operating near VT may also increase data setup times, thus degrading the maximum operating speed.

WDC publishes the VIH spec for a reason, and really you want the incoming logic-high level to be at or

above VIH. Although VT is only slightly above 2.4V, the shortfall from 2.4V to VIH is

not trivial. I suspect there aren't many TTL-output devices which overperform to this extent. This means noise immunity is likely to be compromised, and perhaps maximum clock frequency as well.

I don't feel this unhappy situation deserves to be called TTL compatibility! It is a second-tier solution, not to be confused with the optimal compatibility an engineer would prefer.

-- Jeff

Note: my limited testing of 65xx CPU's can't be used to predict the transition voltage for all extant specimens. Also, the subject of TTL Compatibility involves current as well as voltage, and outputs as well as inputs. But I have focused only on the

voltages accepted by CPU

inputs because that's by far the most controversial and problematic aspect.