Drass and Jeff: putting CMOS output in parallel, nice going.

//I still wonder if clock buffers/distributors could distribute data signals as well... and if their outputs could be wired together.

:---

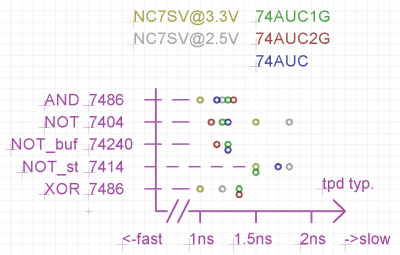

Now for some boring statistics: Fairchild\Onsemi NC7SV versus TI 74AUC.

Propagation delays of different logic chips, load = 30pF parallel 500 Ohms to GND, 25°C.

Format is "min. / typ. / max." in ns.

When typ. was not specified, I assumed typ. = (min. + max.) /2 and added a question mark.

//1 gate per chip

NC7SV08:

2.3V..2.7V: 0.8 / 1.2 / 2.6,

2.7V..3.6V: 0.7 / 1.0 / 2.3

NC7SV14:

2.3V..2.7V: 0.8 / 1.8 / 3.7,

2.7V..3.6V: 0.7 / 1.5 / 3.3

NC7SV86:

2.3V..2.7V: 0.8 / 1.2 / 3.6,

2.7V..3.6V: 0.7 / 1.0 / 3.3

//1 gate per chip

74AUC1G08: 2.5V: 0.5 / 1.25? / 2.0

74AUC1G14: 2.5V: 0.5 / 1.5? / 2.5

74AUC1G86: 2.5V: 0.7 / 1.35? / 2.0

//2 gates per chip

74AUC2G08: 2.5V: 1.0 / 1.3? / 1.6

74AUC2G14: not available.

74AUC2G86: 2.5V: 0.7 / 1.35? / 2.0

//4 gates per chip

74AUC08: 2.5V: 0.5 / 1.15? / 1.8

74AUC14: 2.5V: 0.7 / 1.7? / 2.7

74ACU86: not available.

;---

Sorted for speed, based on typ. propagation delay:

NC7SV08@3.3V:1.0 > 74AUC08:1.15? > NC7SV08@2.5V:1.2 > 74AUC1G08:1.25? > 74AUC2G08:1.3?

NC7SV14@3.3V:1.5 = 74AUC1G14:1.5? > 74AUC14:1.7? > NC7SV14@2.5V:1.8 //74AUC2G14 not available.

NC7SV86@3.3V:1.0 > NC7SV86@2.5V:1.2 > 74AUC1G86:1.35? = 74AUC2G86:1.35? //74AUC86 not available.

And the winner for Schmitt trigger inverters, AND and XOR is +3.3V powered NC7SV.;---

Edit:

Requested by Jeff down in the thread:

NC7SV04@3.3V: 0.7 / 1.5 / 2.3

NC7SV04@2.5: 0.8 / 1.8 / 2.7

74AUC1G04: 0.5 / 1.2? / 1.9

74AUC2G04: 0.7 / 1.1? / 1.5

74AUC04: 0.5 / 1.25? / 2.0

NC7SV240: not available.

74AUC1G240: 0.8 / 1.25? / 1.7

74AUC2G240: 0.6 / 1.15? / 1.7

74AUC240: 0.9 / 1.25? / 1.6

74AUCH240: 0.9 / 1.25? / 1.6

The winner for inverters is +2.5V powered 74AUC2G04.Attachment:

cmos_propagationdelay.png [ 48.22 KiB | Viewed 2379 times ]

cmos_propagationdelay.png [ 48.22 KiB | Viewed 2379 times ]

;---

Just for the fun of it:

//-5.2V NECL from the 80s (obsolete):

//MC10H113 (4* XOR): 0.40 / 1.05? / 1.70

//MC10H104 (4* AND): 0.45 / 1.10? / 1.75

//fully differential 3.3V..5V PECL with chips from 2020:

//MC100EP05 (1* AND): 170ps / 220ps / 270ps

//MC100EP08 (1* XOR): 180ps / 250ps / 300ps

//CML and "don't look for the price": AnalogDevices.

//HMC726 (1*AND): 95ps typ. //13 Gbps

//HMC725 (1*XOR): 105ps typ. //13 Gbps

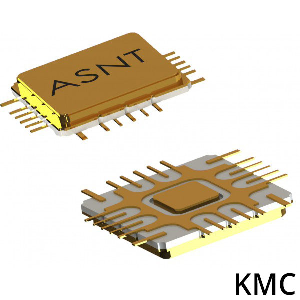

//CML and IDKFA: Adsantec, the computer probably would be as expensive as a Cray-1 then.

//ASNT5160 (1* AND): 50 Gbps, 25GHz

//ASNT5143 (1* XOR): 32 GHz

Attachment:

adsantec_package.png [ 78.3 KiB | Viewed 2455 times ]

adsantec_package.png [ 78.3 KiB | Viewed 2455 times ]