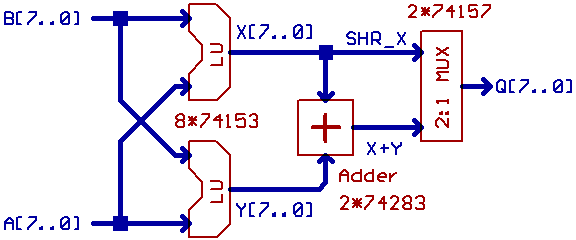

I think I should elaborate my idea for a different ALU design more detailed.

Drass, what we currently have in the CPU are 74153 4:1 multiplexers,

working as logic units, feeding the inputs of 74283 adders:

;...

What I'm suggesting is related to the _other_ ALU design described

here,

except that the SHR MUX is missing this time.

;---

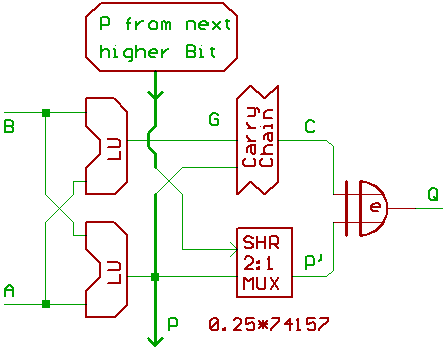

My suggestion is tossing the 74283 out of the design.

One 74153 contains two 4:1 mutiplexers, which are working as LUs (logic units), emitting the P (propagate) and G (generate) signal for one Bit of data.

(Means, that the ALU control signals for the multiplexers have to be different than they are now.)

The P,G outputs of the two multiplexers per data Bit go to a NC7SB3257 FET switch, 4 FET switches required for 4 Bits of data,

and that's the carry chain.

We need one two input XOR gate per data Bit for generating the ALU output from P and carry, and that's all.

//Maybe tossing the 74283 out of the incrementer\decrementer would make sense, too.

;---

For the two input XOR gate, to me two chips look interesting:

NL17SZ86NC7SZ86It's a pity, that there seem to be no XOR gates with three_state output.