Would be nice, if you could tell us how many experience with hardware tinkering you already have,

to avoid digging too deep into some boring basics.

Now for some more boring basics.

Attachment:

edge_boring_basics.png [ 54.86 KiB | Viewed 12635 times ]

edge_boring_basics.png [ 54.86 KiB | Viewed 12635 times ]

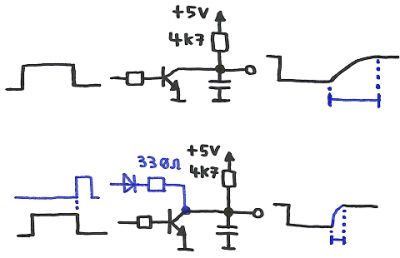

"Open collector" means, the driver only is able to switch the output pin to GND.

For 74LS, it's something like a bipolar NPN transistor as in the picture above.

For 74HC(T)\AC(T), it's a FET instead, but the concept remains the same.

The 74125\74126 buffer has a push/pull output, means there is (at least) another transistor

for sending current from VCC into the output too...

but when connecting the input of the buffer to GND and just tinkering with the output enable,

the buffer just works like a 7405 or such.

(There are chips like 7405 with an open collector output,

but sometimes they are not available as AC(T), and 74125\74126 gives a nicer PCB layout.

That's why I had used 74125 and 74126 in my experiments).

But back on topic:

To have a logic high level at an open collector output in case the output isn't switched to GND

by the output transistor, we also need a pullup resistor (4k7 in the picture),

pulling the output to a logic HIGH level.

And that's where the problem starts if you try aiming for speed:

Because of the output resistor, the falling edge of the output signal will be fast,

but the rising edge of the output signal is slowed down by the value of the pullup resistor

and the capacitive load attached to the output pin (as resistor plus capacitor are forming

sort of a

"low pass filter").

There is a limit for making the pullup resistor smaller:

Output transistors of a NMOS 6522 or 6526 probably can't pull much current to GND,

so the voltage at the output won't reach logic low level if too much current goes through the pullup resistor.

(Imagine a scenario, in which you have a C64 with a TTL 6526, with a fast loader parallel cable

which goes from that 6526 to an old NMOS 6522 inside the 1541 floppy drive).

An alternative to having a smaller pullup resistor when trying to improve rise time of the output signal

would be to "inject" some current for a short moment, let's say half a PHI2 cycle

(the blue diode and the blue resistor in the picture above).

Haven't tested this idea, of course, so I can't tell how old NMOS chips would like this approach.

;---

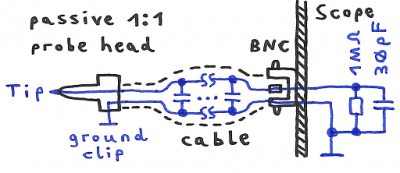

But back on the capacitive load in the picture.

Attachment:

probehead.png [ 85.25 KiB | Viewed 12635 times ]

probehead.png [ 85.25 KiB | Viewed 12635 times ]

When attaching something like a 1:1 logic probe to the open collector output,

you have the capacitance of the scope plus the capacitance of the cable.

(I'm simplifying things a bit here).

When attaching some circuitry to the open collector output,

you have the capacitance of the PCB traces to GND (and/or between the traces),

plus the capacitance of the IC input pins which are tied to that output.

You don't need to know the boring basics about the innards of

scopes and

TTL chips, of course.

;---

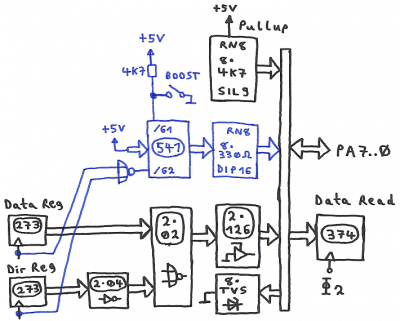

Now for a block diagram for an 8 Bit open collector output port:

Attachment:

port_opencollector.png [ 225.07 KiB | Viewed 12635 times ]

port_opencollector.png [ 225.07 KiB | Viewed 12635 times ]

Be warned: That blue marked speedup stuff only is hypothetical and untested.

Remembering my TTL 6522 experiments, there is a latch for reading what's on the port,

and it samples at the rising edge of PHI2...

and I think that the designers intentionally had built it this way for better noise immunity.

About that little box labeled

TVS: that's just protection diodes for clobbering down transients.

When trying to drive long lines at higher speeds, adding such diodes might be a good idea.

Too much text, loo little time, if you have some questions please feel free to ask.