Hi everyone. I'm back to "work" after a mandatory two months break, due to some family stuff going on (Nothing bad! Some good stuff actually, that needed my attention for some time).

And today, I bring a story of failure and success. I left here:

Quote:

When a ForceLoad is issued to a timer, when counting anything other than PHI2, if the ForceLoad is done one cycle before the timer underflow, the underflow is missed, and so is the interrupt.

Right before this little break, I found a possible solution to this issue that worked, at least on logisim. In order to create the counting pattern found in the timers, (Remember, no 0 is ever read, but on reload, the starting value could be read twice : 4-3-2-1-4-4-3-2...) Whenever an underflow happens, a clock is removed from the pipeline the very moment the reload is triggered.

However, this same clock was being removed on any timer reload. If timer is stopped, a write to THI triggers a reload. This is not a problem as the timer is not running here.

Also, when a ForceLoad is issued, the pipeline was also cleared, and this, is what's preventing the interrupt to fire. So by not resetting the pipeline on a ForceLoad, the issue should be fixed.

The only downside is that this requires ForceLoad to be delayed one cycle, requiring a new FF.

Back from the break, I devised a way to upgrade my current B1 Board from its current form (v0.1.1) to the version with this fix included, (v0.2.1).

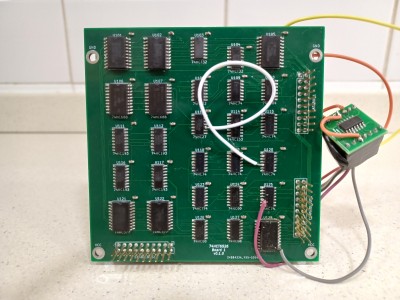

Attachment:

20230319_prefix.jpg [ 2.39 MiB | Viewed 5254 times ]

20230319_prefix.jpg [ 2.39 MiB | Viewed 5254 times ]

This is how the board looked before starting the conversion. There's already an extra FF hanging from the board, with the second FF on the IC used by another fix in the ICR... So ugly!

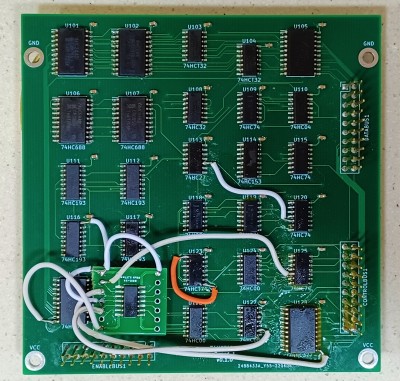

Attachment:

20230319_step1.jpg [ 1 MiB | Viewed 5254 times ]

20230319_step1.jpg [ 1 MiB | Viewed 5254 times ]

Much better now. This is in fact the same version as before, but with a dedicated 74HCT74 for B1. I also tidied up the wires on the board.

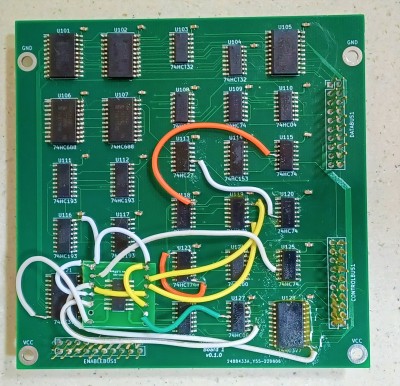

Attachment:

20230319_step2.jpg [ 893.88 KiB | Viewed 5254 times ]

20230319_step2.jpg [ 893.88 KiB | Viewed 5254 times ]

And the, the final version, with the second FF added to delay ForceLoad, and with a few cut traces and bodge wires to amend my problems.

Now, time to test comes.... and with it, a sounding failure.

I first tested the full stack on my SBC6526. All good, hopes are high. Time to test on a C64... and boom. Nothing works. The whole stack misbehaves. Failures are intermittent. It kinda works... for a few tests then everything falls apart.

All the work has been done on B1, so I removed all the bodges, reflow all the ICs, added and rechecked all connections... and I was getting the same misbehaviour!

After two days of headbanging against the walls and no progress... I decided to give the board a deep and nice cleanup. All the works I've been doing, there was flux all over the places.

Unexpectedly, everything worked. It seems all the flux on the board was adding enough resistance that the LS logic in the C64 was not able to handle it, but all the CMOS parts in my SBC could.

So... clean your flux! That was two days lost! Shame on me!

But after the clean up... the success. With all the changes to B1, everything still is as cycle accurate as it was before, which is amazing. I still have the issue with the missed interrupt, just because it's TIMERB the one skipping it. I chose to make the changes to TIMERA first, as the board was already heavily modified.

Now it's time to introduce the changes into TIMERB. Hopefully, it will allow me to pass this first test.

All this fixes are introduces in v0.2.1, which is not published yet. Once I test it on TIMERB, if it works, it will be commited to github.

Now... more bodging!

Cheers!