Hi all!

I've got it

The AM/PM fix was trickier than expected, but still doable.

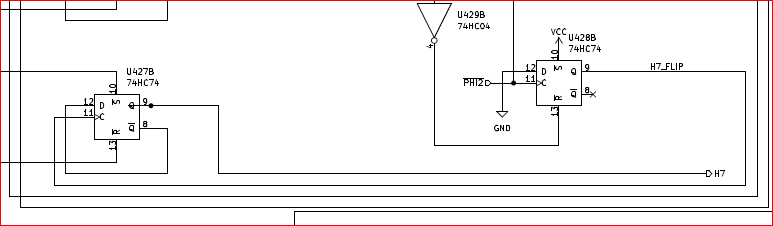

This was my starting point

Attachment:

AM_PM_FLIP_issue.png [ 9.93 KiB | Viewed 2183 times ]

AM_PM_FLIP_issue.png [ 9.93 KiB | Viewed 2183 times ]

Let's recap. The FF on the left holds the AM/PM bit (TODH7). The input to the inverter U429B is a signal than goes high, whenever 12 is on TODH (Ignoring TODH7). The FF on the right should go high whenever TODH7 has to flip (at 12) but it was incorrectly wired. It never went high.

To fix this the data input has been rewired to VCC (So the FF is always high, until resetted by the 12 hour signal). Also the H7_FLIP signal was rewired and now comes from /Q. When we had 12 in TODH, H7_FLIP went high and flipped the AM/PM bit. Success!!!!

Nope. Not yet.

What I said above is indeed true, but there's another scenario that flips AM/PM. When a 12 is written into TODH, the flag flips, so 92 ends up there. When 92 is written, same thing happens, and 12 is there.

The /SET and /RESET inputs of U427B go low when a 1 is written to TODH7, or a 0, respectively. When a 12 or 92 are written to the TODH, the H7_FLIP signal goes high, but the /SET or /RESET prevail so the flip does not happen.

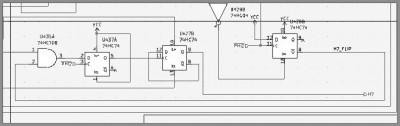

To fix this, I had to insert another FF to delay H7_FLIP by one cycle. And now, when I write 12 I get 92, and when I write 92, I get 12. Success!!

Nope, almost there, but still...

Let's suppose I write 12 to TODH. 12 get stored in the register. H7_FLIP goes high (As its FF /RESET goes low). Then it gets delayed by one cycle, and flips TODH7, resulting in the expected 92.

What happenes if I write 12 again? I get 12, because, the H7_FLIP FF never comes out of reset. So... I ANDed H7_FLIP with the /LOADH signal (The write register signal). So, if H7_FLIP is high, and we write another 12... H7_FLIP, flips again.

Success??

Yes. Now my TOD reflects the real TOD behaviour.

Attachment:

ampm_fix.jpg [ 33.19 KiB | Viewed 2183 times ]

ampm_fix.jpg [ 33.19 KiB | Viewed 2183 times ]

And with this, all the unit tests I've got work. Keep in mind these tests don't go too deep, so this only means it more or less work, but it doesn't mean I'm cycle exact. So, what are the next steps?

- Find out what's going on with SDR. Still not sending, and so far, I'm clueless. It did work before so it shouldn't be too difficult to find out what's wrong, but it's resisting.

- Build the second TOD, to complete the second 74HCT6526

- Remove and socket second CIA on my C64

- Complete all VICE Tests. These do go deep. In fact, passing all tests, pretty much guaranteed a complete and cycle exact 6526.

- Plug both 74HCT6526s into the SBC6526... and crank up the clock! Let's see how far this thing goes.

Somewhere along the way, a v0.2.3 will be released will the latest changes. Also, I do not forget that my TOD does not replicate the invalid count cycles. And improved TOD should be done at some point too.

Ahh... Do you feel that? It's completeness, and I like it very much.