Hi everyone.

Slow but steady progress here. I've spent the weekend further diagnosing ISSUE 5:

5. B12. CNT counts two pulses. OneShot mode counts one additional tick. U10B seems to be updated after the counter has ticked.

It turned out to be not one, but two separate issues.

If you take a look at the "Decrement and Load" portion of the schematic.

download/file.php?id=9002&mode=view(Shown here is Timer A, Timer B has an additional MUX, as it has more timer input options, but it's irrelevant here)

The oneshot additional tick was solved by clearing the last FF on Underflow, just tying U10B /CLR to FORCELOAD. However, CNT pulses are still counting double, even triple sometimes.

First of all, I've had to add a rising edge detector (made with a flipflop) before U9B. Before this, the timer was ticking every PHI2 cycle if CNT was held high, instead of counting just rising edges. Still, this doesn't fix the double count, although it was something needed.

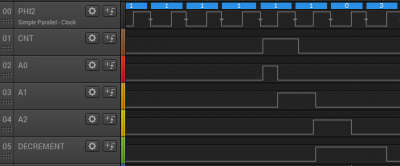

I've taken some samples with a logic analyzer of the output of the 4 FFs in the chain.

U9B output is A0

U9A output is A1

U10A output is A2

U10B output is DECREMENT.

As U9B goes high for a single cycle whenever there's a rising edge on CNT, you (or at least I) would expect to see a pulse, one cycle wide, going through the pipeline on each PHI2 cycle. And indeed, sometimes I got it

Attachment:

cnt_pulse_ok.PNG [ 21.42 KiB | Viewed 1405 times ]

cnt_pulse_ok.PNG [ 21.42 KiB | Viewed 1405 times ]

But, most of the time (over 90% I'd say) this is what I see

Attachment:

cnt_pulse_notok.PNG [ 20.78 KiB | Viewed 1405 times ]

cnt_pulse_notok.PNG [ 20.78 KiB | Viewed 1405 times ]

U10B goes high at the same time as U10A. I haven't been able to find any explanation so far. I've checked the obvious. Verified the soldering, replaced U10 just in case it was bad, tested both TIMERA and TIMERB boards. Same exact result.

The only idea I have right now, is that U10A is getting updated before U10B handles the clock tick, so when the clock reaches U10B, U10A is already high. Considering both FF are on the same IC, both clock pins are separated by a trace no more than 3mm long, so, unless this is happening inside the IC... it escapes me. It's worth noting the first two FF in the pipeline are in reverse order (First B, then A). Of course, datasheet for the 74HCT74 states a minimal propagation time, between the clock pulse, and the output changing of 15ns, so the only idea I have seems to be just not possible.

But... I'm getting there... I'll get there

Cheers!