I've been given some re-marked CPU's to play with, and I've been trying to work out what they really are.

Attachment:

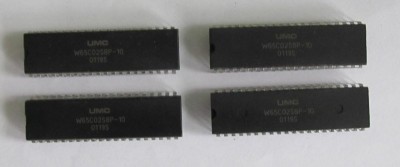

File comment: 4 NOS devices all with the same lot code, and only 1 set of mould marks. Hmmmmm

re-marked chips.jpg [ 26.55 KiB | Viewed 3335 times ]

re-marked chips.jpg [ 26.55 KiB | Viewed 3335 times ]

One thing they're not is CMOS 65C02s, of the 4, 3 will start up and run 6502 code on a test board. All 3 exhibit the JMP (xxFF) bug so have an NMOS core of some description. The test board is wired for a modern W65C02, but has an additional jumper to add 0v to pin 1 in place of VP.

Attachment:

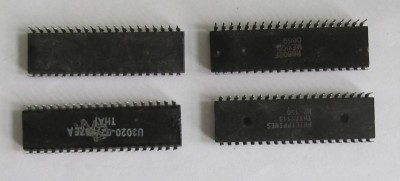

File comment: Reverse view is interesting

under sides.jpg [ 34.38 KiB | Viewed 3335 times ]

under sides.jpg [ 34.38 KiB | Viewed 3335 times ]

The under side shows how little care was taken with the re-marking. While the top's been sanded and etched, they've not bothered to "clean up" underneath.

Top left, with no rear markings, that's one of the one's that works, it ran the basic diagnostics at 1 and 4mhz. Other than knowing it's NMOS, and probably a 2mhz part, there probably not much more can be found out.

Top right, that's the one that doesn't work in the test board, with or without 0v on pin 1. The markings are interesting, the look like something Rockwell might have printed, but R6502F ? Close up, the print looks old, the solder splashes and marks from the removal process go over the print. There's no evidence I can see that the last letter is misprinted or altered. I could be underneath it's nothing like a 6502 CPU, or it is (was), and is dead. If it is a custom 6502 design of some type, it might be interesting to find out more.

Bottom left, the printing matches a picture I found of the SYU6502A. Like the others, tested as NMOS and ran at 1 and surprisingly since that's a 2mhz part, it completed the tests at 4mhz.

Bottom right, the only one with mould marks, the text font and format look like something out of CSG but I've not located any pictures with a close match to make a guess as to which one of the myriad of CPU versions it is. It runs the test code at 1, 2 and 4mhz. No surprise that it failed a 6mhz.

So:

Any ideas about how to identify the "CSG" chip if that's what it is

Likewise the "R6502F"

The test board is point to point soldered, so wiring up additional pins isn't a problem.