Hello all,

Sigrok is a cross-platform, open-source signal analysis suite that supports a

wide range of test devices (scopes, logic analyzers, multimeters, etc.) It has a graphical front end (called pulseview) and a command line interface (called sigrok-cli). Both of these use a common backend (called libsigrok) that contains the capture hardware specific drivers. It also supports a wide range of

protocol decoders, ranging from simple serial protocols (e.g.

RS232 and

SPI) to complex processor bus analyzers (e.g.

ARM and

Z80). But unfortunately no support for the 6502.

So a couple of weeks ago myself and BigEd set out to remedy that by trying to write a 6502 protocol decoder.

I've written up the adventures as a set of posts over on stardot, entitled Open Source Logic Analyzer Experiments:

-

Part 1: An Introduction to Sigrok and Logic Sniffer-

Part 2: Probing the 6502 with Sigrok-

Part 3: Writing a 6502 Protocol Decoder-

Part 4: Synchronous capture, triggers and sigrok-cli-

Part 5: Using an uber-cheap FX2LP development board-

Part 6: Simplifying capture on the Beeb Model B (added 20th Nov 2017)-

Part 7: Using Sigrok-cli / FX2 Logic Analyzer / 6502 Decoder on Windows (added 7th Feb 2018)Rather than simply repeat all that here, I'll pick out some highlights.

The 6502 protocol decoder requires just 12 signals plus ground to be connected: D7..D0, RnW, Sync, Rdy and Phi2. From these, it's able to produce full instruction traces:

Code:

mos6502-1: ????: INTERRUPT!!

mos6502-1: E364: LDA #40

mos6502-1: E366: STA 0D00

mos6502-1: E369: SEI

mos6502-1: E36A: LDA #53

mos6502-1: E36C: STA FE8E

mos6502-1: E36F: JSR E590

mos6502-1: E590: LDA #0F

mos6502-1: E592: STA F4

mos6502-1: E594: STA FE30

mos6502-1: E597: RTS

mos6502-1: E372: JMP 8020

mos6502-1: 8020: LDA #FE

mos6502-1: 8022: TRB FE34

mos6502-1: 8025: STZ DFDD

mos6502-1: 8028: TRB 0366

mos6502-1: 802B: CLD

mos6502-1: 802C: LDX #FF

mos6502-1: 802E: TXS

mos6502-1: 802F: STX FE63

This was produced from sigrok-cli, and you might recognise it as the first few instructions of a BBC Master after reset.

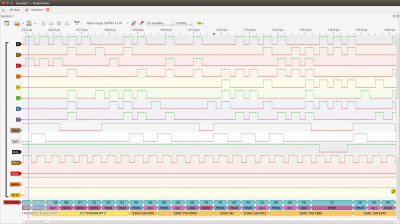

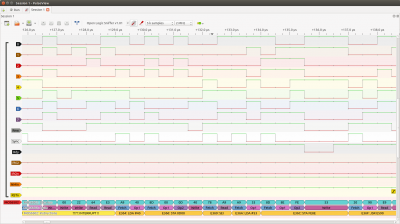

It's possible to capture the same data graphically using pulseview:

Attachment:

sigrok20.png [ 187.68 KiB | Viewed 12236 times ]

sigrok20.png [ 187.68 KiB | Viewed 12236 times ]

Zooming in slightly, you can see we have annotated individual bus cycles.

Attachment:

sigrok21.png [ 138.37 KiB | Viewed 12236 times ]

sigrok21.png [ 138.37 KiB | Viewed 12236 times ]

You can see each instruction starts with a fetch cycle, followed by optional operands, then finally any memory accesses. At least most of the time, as JSR is a little different. You can also see that the Master makes use of RDY to extend reads and writes to certain I/O addresses.

What's quite neat here is that even without any connection to the address bus, the protocol decoder very quickly starts predicting what the current program counter value would be. The algorithm for doing that (mostly down to Ed) is

here.

In terms of capture hardware, this should work with anything that is supported by Sigrok that has at least 12 channels and can sample at ~5x the CPU speed. I've tried out a couple of different logic analyzer implementations:

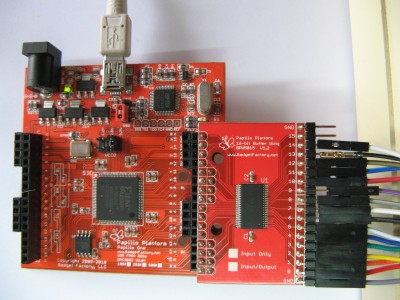

The first was a version Open Bench Logic Sniffer that I recompiled for my Papilio One FPGA board:

Attachment:

IMG_1121.JPG [ 443.19 KiB | Viewed 12236 times ]

IMG_1121.JPG [ 443.19 KiB | Viewed 12236 times ]

This supports sampling at up to 200MHz, and allows for synchronous sampling (where Phi2 is used as the sample clock). But it stores samples in FPGA block RAM, so the capture depth is quite limited (a couple of thousand instructions).

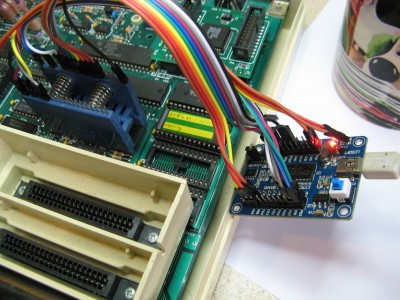

The second was a cheap (£12.49 from

here) Cypress FX2 development board:

Attachment:

IMG_1124.JPG [ 473.68 KiB | Viewed 12236 times ]

IMG_1124.JPG [ 473.68 KiB | Viewed 12236 times ]

This streams data directly to host memory, so supports much longer captures. But it's limited to 12MHz sampling, and doesn't support synchronous sampling. I've successfully captured in excess of 2 million 6502 cycles, which is more than enough for the complete startup of the BBC Micro.

Both interfaces work very well in practice, and the 6502 protocol decoder supports both synchronous and asynchronous sampling (based on whether Phi2 is wired up or not). A decent 40-pin DIP clip is highly recommended, as most cheap test grabbers are absolutely rubbish.

The source code for the protocol decoder is available in github:

https://github.com/hoglet67/libsigrokde ... rs/mos6502I can't really overstate how useful a tool like is can be in diagnosing misbehaving 6502 systems (old or new). If anyone wants to have a play, I'm quite happy to help answer any questions. Deployment should just be a case of copying these three files into the right place in your sigrok installation. There are a few more details in the stardot posts (linked above)

Dave