Back in 2012, Thomas ’skoe’ Giesel did a very nice PDF about reverse engineering the PLA

which does the address decoding in a C64:

http://www.zimmers.net/anonftp/pub/cbm/firmware/computers/c64/C64_PLA_Dissected.pdf;---

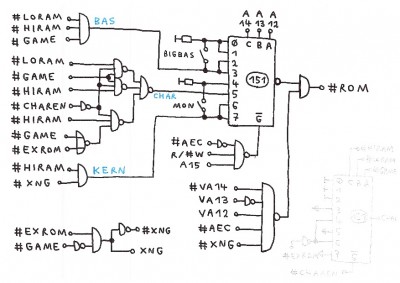

For supporting the C74 project, I felt a need to dig into those PLA equations and to try

drawing something like a TTL styled schematic, I'm not sure if the results are correct so far.

It's just for estimating the amount of logic and chips required for getting the functionality...

didn't try to optimize for size or speed.

IIRC the C64 has separate ROMs for BASIC, KERNAL, and character set.

Each one of those ROMs has a chip select signal.

Be warned, that for my decoder, I assumed that there is only one 32kB ROM containing all the

binary images of the ROMs in the C64, with only one chip select signal labeled #ROM.Note, that in the C64 AEC is inverted by U8 (74LS06 with a 180 Ohm pullup resistor at the open collector output)

before it enters the PLA. The inverter is in the North West corner of

this schematic.

The timing in a C64 is "a little bit tricky", means that if you (hypothetically) would try to replace the PLA in a C64

with a lump of TTL logic, better make sure that your contraption has the same propagation delays as the original PLA,

nothing more, nothing less. Else, there is a danger that your C64 won't be running stable.

;---

Attachment:

c64_addrdec_1.jpg [ 135.48 KiB | Viewed 5186 times ]

c64_addrdec_1.jpg [ 135.48 KiB | Viewed 5186 times ]

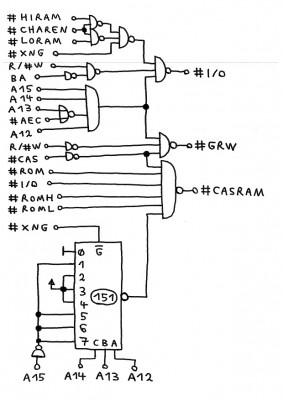

Attachment:

c64_addrdec_2.jpg [ 108.34 KiB | Viewed 5186 times ]

c64_addrdec_2.jpg [ 108.34 KiB | Viewed 5186 times ]

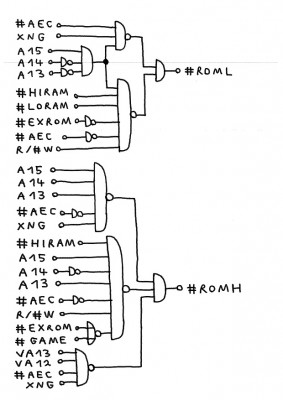

Attachment:

c64_addrdec_3.jpg [ 106.61 KiB | Viewed 5186 times ]

c64_addrdec_3.jpg [ 106.61 KiB | Viewed 5186 times ]

Attachment:

c64_pla.txt [16.6 KiB]

Downloaded 452 times

c64_pla.txt [16.6 KiB]

Downloaded 452 times

;---

If one would (hypothetically) have a 6502 compatible CPU with a 24 Bit address bus,

those TTL schematics would need to be modified to have ROM and I\O only in the lowest 64kB block of memory.

For my schematics, I

guess (as in 'I didn't do any math for getting the exact numbers')

that implementing them the way they look like now would take ca. 17 TTL ICs, and from the propagation delays

it might be difficult to run that (hypothetical) CPU at more than maybe 12 MHz (even when using 10ns SRAM).

BTW: not supporting a cartridge by tossing out the signals #GAME, #EXROM, #ROML, #ROMH

probably would reduce the size of those schematics by 50% or so.

;---

Another approach of building a fast C64 styled address decoder would be using a fast 10ns RAM

containing a lookup table as an address decoder, but initializing that address decoding RAM after

power_up would be a different topic... BTW: TI has nice bus switches.

Since we are at it: the fastest ROM available would be at maybe 45ns, so when having more than 64kB

of 10ns RAM I think it would be a good idea to be able to "shadow" that ROM in just another 64kB RAM block.