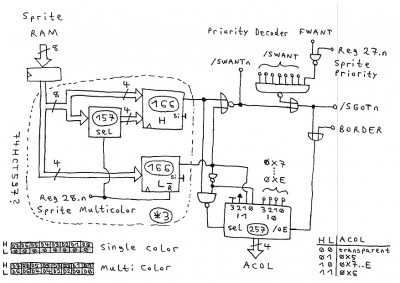

Tried to stick with the concept of using pre_formatted data for the sprites, too.

This would require two shift registers 24 Bit each plus three latches 8 Bit per sprite...

Note, that the serial input of the 74166 shift registers is tied to GND.

If we assume, that nobody would be switching the sprites between "normal" and multicolor

within a raster line, we even could make use of the pre_formatting data multiplexers

in the previous schematic.

For "single color", the L shift register is forced to zero.

Dang, that scanner had switched to monochrome... just take a look at the blue marked

data Bit patterns at the previous page.

That 7430 with the /SWANT signals is for building a sprite display priority decoder.

With /SWANT=0, the sprite says "I want priority".

With /SGOT=0, the sprite says "I got priority".

In theory, one could go without the latches by building 25 Bit shift registers,

means three 74166s and a 7474 at the output in a row.

The trick is to clear the 7474 when loading the 74166s.

But this concept probably would require clock gating...

Attachment:

v2_9.jpg [ 137.02 KiB | Viewed 1234 times ]

v2_9.jpg [ 137.02 KiB | Viewed 1234 times ]

Would suggest to build 8 identical modules (that also contain the X/Y comparators etc.), one for each sprite.

Ok, and with this we are "almost" through with the hot part of the VIC-II.

Will try to add the wiring for the sprite display priority decoder and the sprite/sprite collision detection later... but now I need a break.