whartung wrote:

Curious, looking at this, why do you think it's not 8Mhz like the other board? It seems that WDC sells this only to 8Mhz, but the 65c02 can go to 14Mhz?

Perhaps I didn't express it well enough. The information given in the datasheet of the W65C265 (Table 3-4 AC Parameters) is headed with "VDD=5V / 8MHz". The timing specs within this table says "tCYCF = 250ns Min." but this is 4 MHz not 8 MHz! So I am a bit puzzled. Is it just a typo in the heading of that table? Or could it be that the W65C265 is limited to less than 8 MHz? If the other timing specs (worst cases) were correct, then it might last 90ns (tODA) after falling PHI2 until new addresses and data were valid. In case of 8MHz = 125ns cycle time there would no much time left. None of this timing specs doesn't belong

exclusively to the SXB board nor to the new tiny QBX board.

I was simply confused with these specs and that no one else had said something about that in this forum.

This evening I took a scope and did some measurements (using the SXB board, taking signals from J1 XBus816 Connctor):

(The clock frequency is 3,6864MHz)

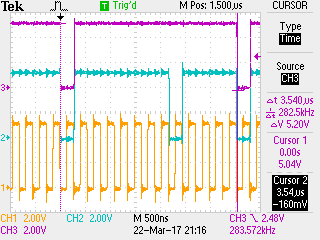

1. an endless loop LDA Long STA Long Jump loop executed out of internal RAM.

Attachment:

File comment: upper trace RWB - mid trace CS7B - bottom trace PHI2

F0005TEK.png [ 76.18 KiB | Viewed 1515 times ]

F0005TEK.png [ 76.18 KiB | Viewed 1515 times ]

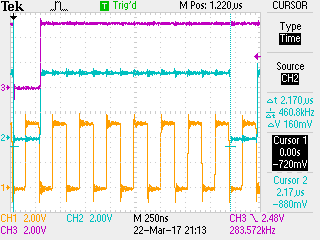

2. same prog, first write access then jump back and read access

Attachment:

File comment: upper trace RWB - mid trace CS7B - bottom trace PHI2

F0004TEK.png [ 76.18 KiB | Viewed 1515 times ]

F0004TEK.png [ 76.18 KiB | Viewed 1515 times ]

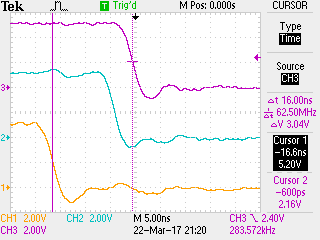

3. closer look to RWB and CS7B become asserted during PHI2 = 0

Attachment:

File comment: upper trace RWB - mid trace CS7B - bottom trace PHI2

F0006TEK.png [ 76.18 KiB | Viewed 1515 times ]

F0006TEK.png [ 76.18 KiB | Viewed 1515 times ]

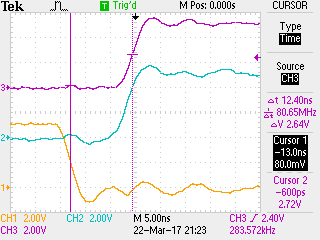

4. RWB and CS7B were deasserted after PHI2 = 1

Attachment:

File comment: upper trace RWB - mid trace CS7B - bottom trace PHI2

F0007TEK.png [ 76.18 KiB | Viewed 1515 times ]

F0007TEK.png [ 76.18 KiB | Viewed 1515 times ]

This looks ways better than what is stated in the datasheet. OK, this way one cannot verify the specs, there are no extreme conditions (temp/voltage/bus load/etc). But at least it gives an idea of whats going on