Some great ideas here folks! Many thanks for that.

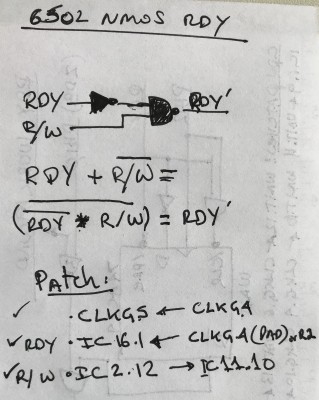

RDY is something that has to be fixed, so for sure it’s a great place to start:

Attachment:

19B0BFB0-9B78-4204-9C5C-746F4AEE00A3.jpeg [ 1.46 MiB | Viewed 4575 times ]

19B0BFB0-9B78-4204-9C5C-746F4AEE00A3.jpeg [ 1.46 MiB | Viewed 4575 times ]

There was an inverter/NAND combination on the board that I could use (previously used for STP), so the patch proved relatively painless. RDY’ above is the NMOS compatible signal — it stays high if R/W is low, which is what we want. In the final design, I’ll want to make the behaviour configurable, but a hard patch will do for now. A quick run with the Analyzer confirmed it works as expected.

But unfortunately, the problems are still there ...

So, onward! Time to see whether illegals or cycle counts are the issue. The TTL CPU conveniently exposes the pins for the current opcode, as well as the internal cycle counter. Using PHI2 as the capture clock, the Analyzer can easily generate a trace dump of all executed opcodes together with the cycles performed. A little validation program then goes through and flags any illegals or cycle-count anomalies. Here is some output of a trace to illustrate. It shows the sample number, the cycle-count (Q) and the opcode info:

Code:

..3e-006 | Q:4 OP:AC,LDY,abs,4

7e-006 | Q:4 OP:AD,LDA,abs,4

9e-006 | Q:2 OP:D0,BNE,rel,2**

1.1e-005 | Q:2 OP:C8,INY,imp,2

3.3e-005 | Q:4 OP:BE,LDX,"abs,Y",4*

3.7e-005 | Q:4 OP:EC,CPX,abs,4

4e-005 | Q:3 OP:B0,BCS,rel,2**

4.4e-005 | Q:4 OP:AC,LDY,abs,4

4.8e-005 | Q:4 OP:AD,LDA,abs,4

5e-005 | Q:2 OP:D0,BNE,rel,2**

5.2e-005 | Q:2 OP:C8,INY,imp,2

5.7e-005 | Q:4 OP:BE,LDX,"abs,Y",4*

6.1e-005 | Q:4 OP:EC,CPX,abs,4

6.4e-005 | Q:3 OP:B0,BCS,rel,2**

6.8e-005 | Q:4 OP:AC,LDY,abs,4

7.2e-005 | Q:4 OP:AD,LDA,abs,4

7.4e-005 | Q:2 OP:D0,BNE,rel,2**

7.6e-005 | Q:2 OP:C8,INY,imp,2

9.8e-005 | Q:4 OP:BE,LDX,"abs,Y",4*

0.000102 | Q:4 OP:EC,CPX,abs,4

0.000105 | Q:3 OP:B0,BCS,rel,2**

Unfortunately (or fortunately??), the games in question show no illegals, and no cycle mis-counts. It’s possible, though, that the CPU still has cycle-inaccuracies where a cycle should be saved but wasn’t. The little validation program would not detect these situations since it just compares against a table of allowable cycle counts for each opcode. Nevertheless, it’s progress, and it’s certainly good to know illegals are not in the mix.

A likely next step is to compare the opcode streams generated with the 6510 and the TTL CPU respectively and see if that reveals anything. Thanks again for the several suggestions above on how to do that!

More to come ...