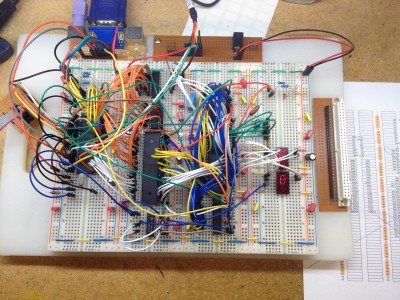

After a series of tests and proof of concepts I finally put all the pieces together and built the first version with all features together on a breadboard. "

ROMulus the

1st", named after the fact that it is my first fully functional ROM less SBC.

Attachment:

File comment: Overview of the breadboard

IMG_0348.JPG [ 3.26 MiB | Viewed 1983 times ]

IMG_0348.JPG [ 3.26 MiB | Viewed 1983 times ]

It has the following features

W65C816 processor, not because it is needed but because it's the only CMOS version I currently have, a CMOS version is mandatory

AS7C1024-20PC 128kbyte SRAM although only 64kbyte are used

VGA text display (supporting 24x40 and 24x80 characters) using a 4k Dual-Port RAM (IDT7134)

PS/2 keyboard

The ROM Image is loaded to the RAM using the IML/blink-load method

The VGA signal is generated using a ATMega1284P. The MCU uses a 22.1184MHz baud-rate crystal. This is also the VGA pixel clock. The VGA timing uses the 640*480@60Hz standard, but with only 560 pixels. A 74HC166 is used as the parallel to serial shift register to create the pixels and a 74HC573 is used as I/O port expansion.

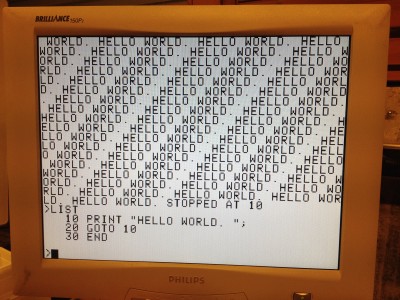

Attachment:

File comment: VGA Display

IMG_0355.JPG [ 3.63 MiB | Viewed 1983 times ]

IMG_0355.JPG [ 3.63 MiB | Viewed 1983 times ]

The 22.1184MHz was selected to

support higher baud-rates (115200baud) for the XModem upload function

support 7-bit wide character ROMs of legacy systems that have patterns which look good only with 7-bits per character

only slightly overclock the MCU

The same MCU also implements the PS/2 keyboard interface. For this the second USART is used in synchronous mode in order to avoid polling or interrupts that could disturb the VGA signal generation. Also the same MCU is used to implement the IML/blind-load feature to initialise the RAM with the ROM Image. For this a 74HC574 has been added that together with the GAL22V10 build the byte buffer that acts as "bootstrap-ROM" during initialisation.

The ATMega1284P has a huge flash (128kbyte) which has room for many more. Currently it contains the code, the CGROM(s) and a 12kbyte 6502 ROM Image which together only occupy 20% of the flash.

The glue logic uses a GAL22V10 and a 74AC00. The GAL implements the key wait flag and the address decoder. The 74AC00 is responsible for the Master-Read and the Master-Write signal (read and write enable signals qualified with PHI2). At the moment the memory map uses the old Apple II scheme and looks like the following

$0000..$BFFF RAM

$C000..$C00F Keyboard Buffer holding the ASCII code in Bits 0..6 and the key wait flag in D7

$C010..$C01F Clear the key wait flag

$C020..$C0FF General IO

$C100..$CFFF RAM for IO support routines, write protected after initialisation

$D000..$FFFF RAM for the ROM Image, write protected after initialisation

I used the Apple II scheme so I could be using the original Apple II ROM (D0,E0, E8, F0, F8 ROMs) giving me time to concentrate on the MCU code first until everything worked. As all the address decoding takes place in the GAL22V10 the memory map can be easily adopted to the final needs without changing the wiring.

The same MCU is also generating the PHI2 clock. During the initialisation it "manually" controls the state of PHI2 to load the ROM image. PHI2 is using OC2B of Timer 2 and once the image is loaded I connect the PIN to the Timer to create the system clock. The maximum system clock that can be created in this way is half the MCU clock rate. I currently run the system at the maximum of 11MHz and it's stable.

The MCU also provides a user interface via RS-232 that allows to perform the most basic system controls.

Reset the 65xx system

Start and Stop PHI2, PHI2 can be set to 11/(N+1)MHz, where N=0..127

Show the system status (VPB, RES, IML, PHI2 when in manual mode)

Download a 6502 image via XModem to the RAM

Load a ROM image in the MCU flash to the RAM

Control IML (Initialisation Mode)

Ouput a value to the keyboard buffer

Single cycle PHI2

You can set an initial command so you do not need a terminal to start up the system.

Next will be the clean-up. First I will create some decent documentation. Then the MCU code needs an urgent restructuring and house-keeping. When this is done I'll start with

ROMulus the 2nd that will have on-board ACIA, VIA and compact flash interface. Also it will use a CPLD instead of the GAL so everything can be defined in software and downloaded to the board.

Cheers

Peter