I bought a

Bus Pirate last year, and recently

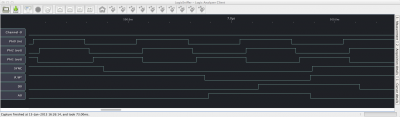

richarde borrowed it. He's just sent me these traces from the pins of a BBC Micro's 6502 - these timings are therefore typical and don't replace the need to study the spec when designing a system.

Attachment:

BBC 6502 Signals.png [ 59.91 KiB | Viewed 1019 times ]

BBC 6502 Signals.png [ 59.91 KiB | Viewed 1019 times ]

However, it's interesting to see what's happening in a typical working system. We note that the phi1 and phi2 signals are indeed (just about) non-overlapping. We think the Bus Pirate is sampling at 100MHz, so there's a quantisation of the edges, and of course the true sample times may be slightly jittered. If anyone can provide traces from an actual logic analyser that would be great.

(This is an NMOS 6502, normally clocked at 2MHz)

Cheers

Ed