So long time no see. Life got severely in the way. Have a step-daughter, and ex-live in, now a wife, and two kids of my own LOL.

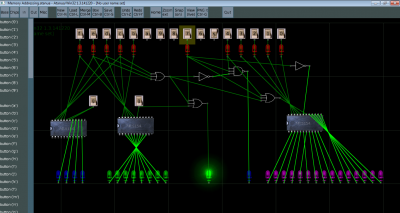

Was going over my notes for what I wanted to build, and been trying to map the memory of the board, so far I have it down to the two attachments. Logic wise it works, based on this simulator, but doesn't mean it would work in circuit. Worried about propagation time.

Made up of 3 74'154, 1 4075 triple OR Gate, 1 74'10 NAND, and 2 NOT gates.

Attachment:

memorymap.png [ 271.06 KiB | Viewed 1052 times ]

memorymap.png [ 271.06 KiB | Viewed 1052 times ]

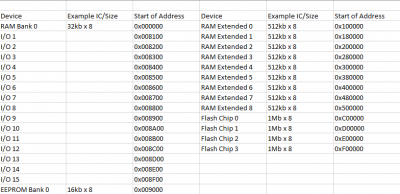

Attachment:

memorymaptable.png [ 24.77 KiB | Viewed 1052 times ]

memorymaptable.png [ 24.77 KiB | Viewed 1052 times ]

Any thoughts?

And yes I realized I wasted a whole bunch of address space in the I/O region, but I figured a single 32kb RAM chip, and a 16kb EEPROM makes it easy to do chip selects, so just went with it to simplify my addressing scheme.

Dimitri