barrym95838 wrote:

Could your overall average trace length benefit from more carefully-considered placement of the components, especially the CPLD and the right-most MAX?

Possibly. The constraints of working within the 21 square inch/650 hole limit of ExpressPCB's Proto-Pro service make it difficult to optimize connections to all devices. When a board is at that size connectors can eat up a disproportionate amount of real esate, the 4-port TIA-232 connector being one such culprit.

What you see is the result of several trial layouts, in which I tried to keep routing as point-to-point as possible. However, the present design is not cast in concrete until I actually order PCBs. So I may well play with it some more.

The CPLD tends to be problematic, as it is connected into the rest of the circuit in disparate places. Also, PLCC packages tend to work better with radial connections, which arrangement doesn't fit very well on a narrow board like what you see in the illustration (n.b., DIP packages are actually worse). If I position the CPLD to favor short connections to the MPU, the connections to the expansion port and QUART get longer. If I position it to favor the latter items, then the MPU connections get longer. It's all about compromise, and in this case, I decided to more-or-less centrally locate the CPLD to keep all traces as short as practical.

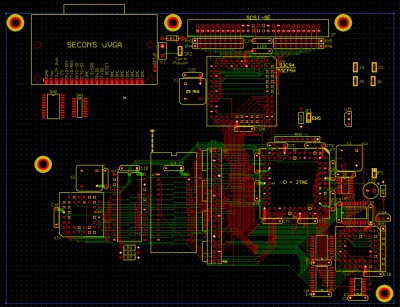

A possibly idealized layout would have the CPLD in between the MPU and the rest of the address and data bus end points (EPROM, RAM, etc.). There isn't enough space on the board to allow such a layout. Another possibility is for the CPLD to be angularly displaced relative to the MPU. The attached illustration, which is a work in progress, has such a layout.

Attachment:

File comment: POC V3 PCB Work-in-Progress

pocv3pcb.jpg [ 2.76 MiB | Viewed 819 times ]

pocv3pcb.jpg [ 2.76 MiB | Viewed 819 times ]

This layout, which is on a truncated micro-ATX PCB, includes Garth's 4MB DIMM, which is to the left of the CPLD, which in turn, is at the top left corner of the MPU. Also, bus drivers/transceivers are part of the design, as the potential bus loading is much higher than my earlier efforts. They are located around the MPU to keep the latter's connections reasonably short.

As for the MAX-238s, their connections operate at the relatively low speed of the TIA-232 signaling rate, no more than 230.4 Kbps in my application. Positioning is non-critical. An alternative that I have considered in place of the two MAX-238s is a single MAX-248, which is essentially four MAX-232s in a PLCC-44 package. However, the single-piece price of the MAX-248 is some 23 USD, versus 15 USD for two MAX-238s. Paying an extra 8 USD to slightly compact the layout seems counterproductive for a hobby computer, no?

I'm always amenable to suggestions, which is why I post this stuff for commentary. Sometimes I don't always see the forest, only a bunch of trees.

Attachment:

File comment: MAX2xx Series TIA-232 Transceivers

LINEDRIVER_max220_max249.pdf [371.61 KiB]

Downloaded 61 times

LINEDRIVER_max220_max249.pdf [371.61 KiB]

Downloaded 61 times