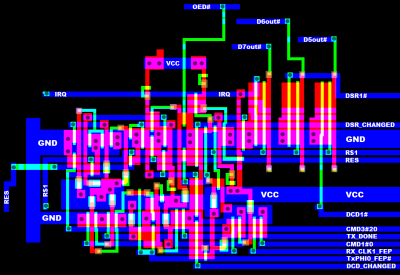

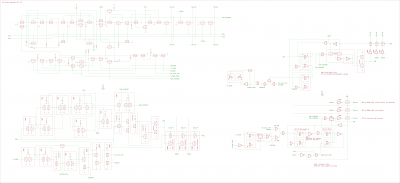

7a) Status register, Bit 7..5

When reading it:

ST7=1 indicates an active interrupt, means that the low_active IRQ# pad is pulled LOW by the 8551.

ST6 gives you what's on the DSR# pad //see "5b) DSR#"

ST5 gives you what's on the DCD# pad //see "5c) DCD#"

Bit 5 and Bit 6 are trivial, so we now focus on Bit 7:

;...

First the TX interrupt:

High active signal TX_DONE, synchronized with TxPHI0_FEP# clock,

goes together with control signal CMD3#20 into an AND gate.

The output of said AND gate basically is the TX interrupt,

which hits after a transmission is done.

TX_DONE is generated in "17) TX control".

TxPHI0_FEP# is generated in "19) TX div16". //TX clock predivider.

CMD3#20 is generated in "12) Control/Command register output decoding".

It is HIGH when CMD3=0 AND CMD2=1 AND CMD0=1.

//TX interrupt enabled, RTS#=LOW, transmitter enabled.

;...

Second the RX interrupt:

High_active signal RX_CLK1_FEP, which is generated in "18) RX div16", //the RX clock predivider

indicates the end of a RX sequence.

It goes together with control signal CMD1#0 into another AND gate.

The output of said AND gate basically is the RX interrupt.

CMD1#0 is generated in "12) Control/Command register output decoding".

It is HIGH when CMD1=0 AND CMD0=1.

//RX interrupt enabled, receiver enabled.

;...

We have two RS flipflops:

First the "RX/TX IRQ sample FF", which samples the RX/TX interrupt.

Second the "RX/TX IRQ FF", which actually is the RS/TX interrupt flag.

RX interrupt and TX interrupt go into an OR gate.

The output of the OR gate sets the "RX/TX IRQ sample FF".

If no Status register read is in progress:

"RX/TX IRQ sample FF" sets "RX/TX IRQ FF".

After "RX/TX IRQ FF" went set, "RX/TX IRQ sample FF" is cleared.

A status register read clears "RX/TX IRQ FF", blocks "RX/TX IRQ FF" set,

and blocks "RX/TX IRQ sample FF" clear.

A hardware reset with RES active also clears "RX/TX IRQ FF".

;...

High_active signal DSR_CHANGED indicates that the logic level at the DSR# pad has changed

from LOW to HIGH (or from HIGH to LOW) since the last Status register read.

It is generated in "5b) DSR#".

High_active signal DCD_CHANGED indicates that the logic level at the DCD# pad has changed

from LOW to HIGH (or from HIGH to LOW) since the last Status register read.

It is generated in "5c) DCD#".

The high_active Q output of "RX/TX IRQ FF", DSR_CHANGED and DCD_CHANGED go into an OR gate.

The output of said OR gate is sampled by a half_static transparent latch

when no Status register read is in progress.

The output of that latch is the IRQ signal which goes to the "2e) IRQ#" pad driver,

and IRQ what you see in Bit 7 when reading the Status register.

;---

Note, that PHI2, RX clock and TX clock are different clock domains.8552 makes creative use of RS flipflops for getting a signal from one domain to the other.

Problem is:

If you are out to do a 8551 FPGA implementation, you won't have RS flipflops.

You probably even would have no transparent latches, but only edge triggered flipflops.

And for the IDE... if you just insert one logic gate into a clock signal path,

the IDE stubbornly will insist that you have two different clock domains at the input and the output,

and it will tread circuitry clocked by the two domains like they happen to be located on two different planets.

So be warned, that you might be getting some more grey hairs there.

Oh, and for a lot of the RS flipflops inside the 8551,

correct functionality of the circuitry depends on the priority for R,S inputs to Q,/Q outputs,

take care.

;---

Attachment:

si8551r2_7a_stat_reg_7_5.png [ 22.07 KiB | Viewed 601 times ]

si8551r2_7a_stat_reg_7_5.png [ 22.07 KiB | Viewed 601 times ]

Attachment:

8551r2_7a_stat_reg_7_5.png [ 95.24 KiB | Viewed 601 times ]

8551r2_7a_stat_reg_7_5.png [ 95.24 KiB | Viewed 601 times ]