Hi Rich,

RichTW wrote:

How are you getting one clock cycle latency?

I've probably confused things slightly by talking about interrupt latency as the time from the falling edge of NMI/IRQ to the start of the 7-cycle interrupt sequence. The minimum interrupt latency, including the 7-cycle interrupt sequence, is actually 8 cycles.

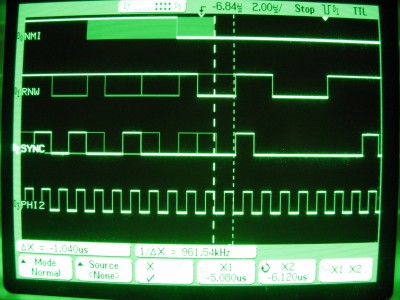

You can directly read the minimum latency off the scope plots (which accumulated many measurements over about a minute). The NMI trace shows all shows all possible points at which NMI was seen to fall prior to the trigger event, which was the interrupt sequence (specifically the 3 cycle write):

Attachment:

IMG_1440.JPG [ 418.51 KiB | Viewed 3848 times ]

IMG_1440.JPG [ 418.51 KiB | Viewed 3848 times ]

The left cursor marks the latest point where NMI was seen to fall, just prior to the interrupt sequence starting. The right cursor marks the Phi2 edge just prior to sync going hi. The difference between these cursors is 1.040us, so a tad over one clock cycle. The trace for IRQ looks pretty much identical.

Your Visual6502 example is interesting, in that it shows 1.5 cycles between IRQ going low and the sync at the start of the 7-cycle interrupt sequence. That's a difference of half a cycle compared to what I see in reality. I guess the explanation is that Visual6502 is only working in whole half cycles, and 1.0 cycles is just too late.

Dave