Just an update on this series of boards, the Micro-PET, Ultra-CPU, and Ulti-PET:

Attachment:

20240525_153100.jpg [ 4.04 MiB | Viewed 1094 times ]

20240525_153100.jpg [ 4.04 MiB | Viewed 1094 times ]

These are essentially Commodore PET clones, but with many more features. This is a family of boards with a set of core features, and different additional features depending on the board variant.

The

Ultra-CPU core is based on my

CS/A bus system, and as an FPGA is used that contains the memory mapping, could be used in different types of system, not just the PET.

The

Micro-PET is the core, plus all the standard PET I/O, mainly IEEE488, keyboard, and tape (but without 9V), on a single 100x190mm board.

The

Ulti-PET finally, is a fully integrated PET clone, with many many features. Most notably, I used the

6502.org original SPI-10 specs and included a 5V (based on the VIA SR), and a 3.3V (based on the FPGA) variant. Also, an UEXT connector is on board, including I2C, 3.3V-TTL serial, and SPI (based on the FPGA SPI interface).

Specs are:

Ultra-CPU:* CS/A bus-based 65816 CPU board

* Up to 17.5 MHz 65816 CPU, with 1MB RAM (512k fast, 512k media RAM)

* 768x576 VGA with 16 colours out of 64, various modes incl. Colour-PET and C64-alike, incl. sprites

* USB host for keyboard and mouse

* DAC (DMA) audio output

* Port for SD-Card adapter (2 variants)

* Port for Network, with either Ethernet or Wifi options

Micro-PET removes the CS/A bus, but adds:

* Standard PET I/O, plus ability to work as IEEE488 device

Ulti-PET integrates, on top of the Micro-PET, the following features from other CS/A bus boards

* (Fast) Serial IEC, incl. ability to work as IEC device, based on the VIA SR

* RS232, plus 2nd TTL serial (shared with UEXT)

* Dual SID with mixer (that includes the DAC audio and the beeper); Speaker amp included.

* Keyboard shift lock / reset (needs Shift lock key on separate keyboard matrix position)

and adds these features on top:

* 2 Joystick ports, switchable between single- and dual mode ("stupid pet tricks" compatible)

* SPI-10 5V, SPI-10 3.3V, and UEXT extension ports (partially shared, see schematics), incl. I2C

* Fully functional Tape incl. 9V for Tape drive power supply

* Expansion ports for the CS/A bus - single wide port, single shortbus port for Ultrabus expansion board

* Accompanying bus extender board to use CS/A, RC2014, Apple-II, or C64 cards

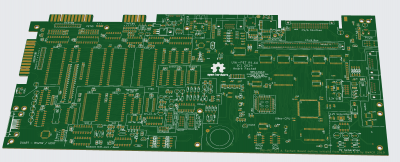

The new revision of the UltiPET going into production:

Attachment:

File comment: picture of the Ultipet board

Ultipet.png [ 279.68 KiB | Viewed 1094 times ]

Ultipet.png [ 279.68 KiB | Viewed 1094 times ]

P.S.: Not all of the boards are already on github, but definitely will be soon. Open Source Hardware.

_________________

Author of the GeckOS multitasking operating system, the usb65 stack, designer of the Micro-PET and many more 6502 content:

http://6502.org/users/andre/