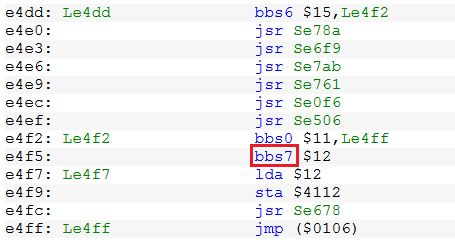

Hello, I think I may have found a small bug. I was disassembling this code, which is "65C02 with bit operations":

Address: $E4DD

6F 15 12 20 8A E7 20 F9 E6 20 AB E7 20 61 E7 20 F6 E0 20 06 E5 0F 11 0A F7 12 A5 12 8D 12 41 20 78 E6 6C 06 01

I get a BBS7 opcode where there should be an SMB7.

Attachment:

bbs7 should be smb7.png [ 9.96 KiB | Viewed 646 times ]

bbs7 should be smb7.png [ 9.96 KiB | Viewed 646 times ]

Code:

$E4DD | 6F 15 12 | bbs6 $15,$E4F2

$E4E0 | 20 8A E7 | jsr $E78A

$E4E3 | 20 F9 E6 | jsr $E6F9

$E4E6 | 20 AB E7 | jsr $E7AB

$E4E9 | 20 61 E7 | jsr $E761

$E4EC | 20 F6 E0 | jsr $E0F6

$E4EF | 20 06 E5 | jsr $E506

$E4F2 | 0F 11 0A | bbs0 $11,$E4FF

$E4F5 | F7 12 | smb7 $12 ; <-- this one disassembled wrong

$E4F7 | A5 12 | lda $12

$E4F9 | 8D 12 41 | sta $4112

$E4FC | 20 78 E6 | jsr $E678

$E4FF | 6C 06 01 | jmp ($0106)

Also, when I load a saved file that using "65C02 with bit operations", it seems to always revert to normal 6502. I just wanted to let you know these things I found; I have worked around them no problem. Thanks for the cool disassembler.