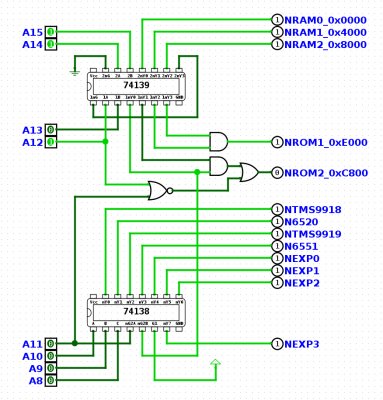

Here's an approach with a few chips that appears to work correctly (though it's certainly not the fastest decode it's only a handful of nanoseconds and should have no issues with a 2MHz clock). Inputs on the left, outputs on the right.

Attachment:

Decode.png [ 72.01 KiB | Viewed 5821 times ]

Decode.png [ 72.01 KiB | Viewed 5821 times ]

Half a '139 is used to initially separate the memory space into four 16k blocks (the N before the output names indicates a low-going output, which is almost always what you want for this kind of thing).

The other half of the '139 is enabled by the 0xc000-0xfff output of the first half, and further decodes that section into four blocks of 4k each. The higher two outputs are ANDed together to give the rom at 0xe000-0xffff, easy, but the other ram is a little more complex since you want to enable it for only 6k of its 8k - the remainder of the addressing is for the IO.

When both A11 and A12 are low, we want to enable the IO and disable the rom: a NOR gate gives a high output at that time which is ORed with the ANDed lower two outputs from the '139.

(Or think of it the other way around: the lower two outputs are ANDed to select 0xc000-0xdfff, and that output is later disabled for 0xc000-0xc800)

The block of 0xc000-0xc7fff is decoded into the eight IO selects by the '138, enabled by both 0xc000-0xd000 being active and A11 being low.

Neil