GARTHWILSON wrote:

Quote:

BigDumbDinosaur wrote:

No pullup resistor is required on RWB, as that output is driven in both directions—it's not an open-collector output.[/color]

It is useful if you use Bus Enable as this pin is tri-stated, but not required.

On a development board, you might want to have an input for BE you can hook a jumper to, just to try it out or experiment with a circuit. In that case, the pull-up on RWB ensures a defined state of the pin. As with most things, it depends on your project goals: some folks here are building optimized production-like boards with a well defined use case. Myself, I'm building something I can play with and learn and I want all combinations of inputs to have defined behavior. It looks like rehsd's board is also more on the experimental side

Great point on the time constant though! Agreed that for this pin to work fast enough you'd need logic driving it.

BigDumbDinosaur wrote:

akohlbecker wrote:

Never said anything about not qualifying them with the clock also

Here is my circuit simulation for read/write pulses (with VA here being VDA OR VPA).

Attachment:

The attachment Screenshot 2022-02-27 at 08.39.03.png is no longer available

In some cases, failure to qualify addresses with VDA may result in a location being touched during a so-called dead cycle. If that location is a chip register, it being touched may cause the device to behave in an undefined way. It has to do with the fact that some addressing modes result in a partially-formed address being asserted before the true address is emitted.

The purpose of VDA and VPA is to qualify addressing, not read/write operations. In a properly-designed 65C816 system, the glue logic will generate a chip select during Ø2 low, since that is when the address bus becomes valid. However, not all bus cycles generate a usable address. That's why VDA and VPA exist.The use case where this is useful is DMA. The address decoding is just a static mapping from portions of memory to a hardware device, but if you introduce signals coming from the CPU side into your decoding, how will the DMA device be able to access memory? it would need to generate VDA/VPA itself. However, these signals can't be tri-stated on the CPU side.

If you instead make the RD/WR pulses depend on VDA/VPA, then the address decoding is static, and any address put on the bus by another device generates the correct chip selects. If you also make RD/WR tri-state via Bus Enable on the CPU side, then the DMA device can generate its own RD/WR signals, and work at any frequency, totally independent from the CPU. The same DMA device could then theoretically also work on any CPU because it doesn't have to know about 65C816 specific signals. It is just a better separation of concerns IMO.

Again, this all depends on what you're building and what your goals are. Most likely sending VDA into a '138 leads to faster logic, if your goal is speed that's great.

Dr Jefyll wrote:

A footnote.

Great points all around, thanks Jeff!

rehsd wrote:

To reduce the number of variables, I removed the RAM and GAL. I am decoding for the ROM enable with A15#. I have changed back to the HC family of ICs for the '573, '245, and '00. I have also added bodge wire to the back of the PCB for all VCC and GND connections for the ICs being used as part of the core 65816.

So far, results are the same. If I keep the ROM CS# connected to GND, reading ROM seems to be fine. If I try to drive the ROM CS# off A15#, ROM reads are not working.

I have attached the current schematic. I uploaded a

video showing what I'm seeing.

Next, I will incorporate VDA/VPA into the simple decode logic.

Forget about VDA/VPA for now, if you can't get your ROM to output data you have bigger problems

Attachment:

Screenshot 2022-02-27 at 23.10.41.png [ 1.62 MiB | Viewed 984 times ]

Screenshot 2022-02-27 at 23.10.41.png [ 1.62 MiB | Viewed 984 times ]

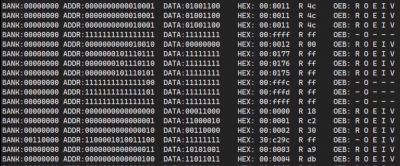

This is an unrelated issue, but your reset vector is not set up properly. Here, the CPU reads from 0xFFFC and 0xFFFD, which both return 0xFF. Then it jumps to 0xFFFF, where it against reads 0xFF. That's a SUB long,X instruction, so it reads the next 3 bytes as data (0x0000, 0x0001, 0x0002 which all return various values). Then it reads 0x30C29C (so at least this means your bank address latching is working, since this is outside of bank 0

)

Then it continues at 0x0003 with 0xA9, which is your LDA #$DB

You probably want 0xFFFC,D to point to the start of ROM at address 0x8000. In this case, the CPU is skipping over your CLC and REP #%00110000 (the CLC makes me think you're also missing an XCE in there to enable native mode?)

I have looked at your updated schematic, and I have not found any problems. How confident are you in your routing? Did you run an ERC check on your design?