I hadn't thought of using it for hardware debugging -- just for software debugging. It never crossed my mind that single stepping could be used for hardware diagnosis until you mentioned it.

Onto the front panel control cards!In theory, they should be self sufficient enough where if you had a device on the bus with an address, you could view the data on that device, with or without a 6502 sitting on the bus. In practice, I've fouled up something well enough that each card works fine on it's own on the test stand, then fails to work find in concert while connected to the bus, talking with other cards.

Attachment:

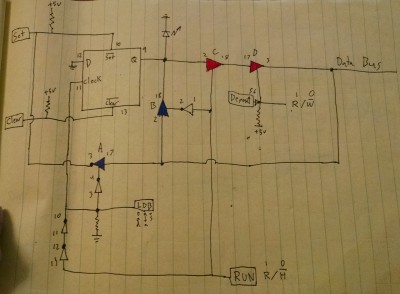

File comment: Data Control Rev 6

IMG_20180313_012217271.jpg [ 1.69 MiB | Viewed 6842 times ]

IMG_20180313_012217271.jpg [ 1.69 MiB | Viewed 6842 times ]

Data Control CardHere we see the fundamental element of the data control card which is far more complicated than it needs to be. This has to be like revision 6 by now. There are effectively 8 of these, one per byte. Thus, there are 8 D-latches acting as RS flip-flops (7474's), and 8 of each tri-state buffer (3x 74244, 1x 74240). The inverters that control the buffers are not duplicated.

The idea is that we can load a value from the data bus into these D-latches. The load signal clears the flip-flop, and then lets any 1's populate their respective flop-flops. Say you made a mistake, and need to change a single bit, you use the set/clear momentary switches to make your changes. This will be visible on the LEDs, while not interfering with the data bus. When you are happy with the value, you can deposit it right back onto the data bus by twiddling the R/W line to make RAM overwrite the new value.

However, all of that is rendered dormant while the CPU is running. One buffer prevents this card from interfering with the data bus. while another buffer now allows the LEDs to directly view data bus activity. The flip-flops are cleared whenever the CPU is running.

Attachment:

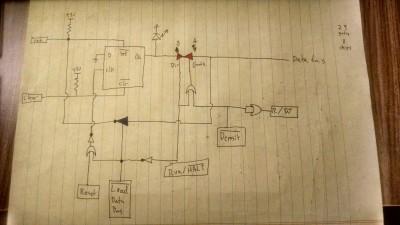

File comment: Data Control Rev 8

IMG_20180319_203629161_HDR.jpg [ 4.11 MiB | Viewed 6842 times ]

IMG_20180319_203629161_HDR.jpg [ 4.11 MiB | Viewed 6842 times ]

I've managed to simplify the design a bit since this point for revision 8, but I'm holding off on building the improved version for the moment. Every time I think I've reduced the complexity on this card (while retaining the same functionality), someone consistently points out a new way for me to improve it (which I should note is more than welcome). Rev 8 doesn't reduce the chip count all that much, but it does reduce the total gates to 29, and eliminates quite a few wires, which makes me happy. I wish I had understood the 74245 sooner.

Attachment:

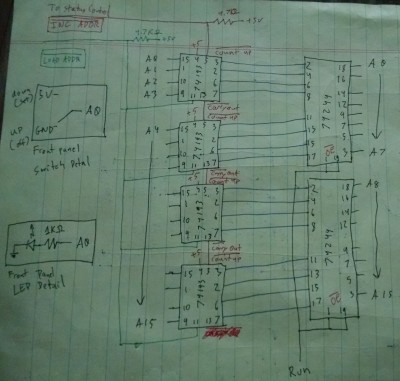

File comment: Address Control

IMG_20180411_051334891.jpg [ 1.7 MiB | Viewed 6842 times ]

IMG_20180411_051334891.jpg [ 1.7 MiB | Viewed 6842 times ]

Address Control CardThis one is probably the most straight-forward card in the bunch. Want to hop to a specific address? Set the toggle switches, and load up that address. Then, you can increment from there to see what is in subsequent addresses. Again, this card has a run lockout to prevent interference when the CPU should be in control of the address bus. The LEDs here are always watching the address bus. Upon typing this, 8 months after assembling the card, I realize I should probably add buffers to prevent extending the address bus lines unnecessarily...

Attachment:

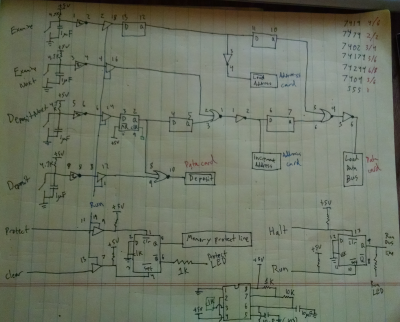

File comment: Status Control

IMG_20180305_062126442.png [ 5.53 MiB | Viewed 6842 times ]

IMG_20180305_062126442.png [ 5.53 MiB | Viewed 6842 times ]

Status Control CardThe status control card feels like a mess to me. It's been revised slightly since this schematic was laid down, but the fundamentals still apply, so for the moment it will do. The job of status control is to pass signals to the data and address cards, letting them know when to Deposit, load the data bus, load the address bus, and increment an address. It also controls weather the CPU is running or halted, as well as if memory is protected (not that this feature works right now). This card became a catch-all for the switches not specific to the data or address cards.

The Examine, Examine Next, Deposit, and Deposit Next momentary switches are all debounced using a simple RC circuit and inverting Schmitt triggers. I only have a cursory understanding of this circuit, as it was suggested to me a few months ago by a friend. Memory Protect, Protect Clear, Halt, and Run instead have toggles, and so I did not include debouncing circuitry. The Step momentary could do with a debounce circuit, but Reset has a DS1233 for the CPU to let it reset cleanly so I'm not worried about it right now.

The complex portion of handling status control is orchestrating the sequence of events needed for things like Examine, Examine Next, and Deposit Next to work right. The timing of these events is determined by a 555 timer and daisy chained D latches that are supposed to ripple down the chain in order. Now that I have a logic analyzer, I want to watch this process happen, step by step.

- Examine tells the address card to load whatever address is on the toggle switches, then tells the data card to load whatever is on the data bus value into the front panel registers to be viewed on the LED indicators. [Load Address] -> [Load Data Bus]

- Examine Next doesn't load from the toggle switches, but instead tells the address card to increment the counters on the address control card, followed by loading the data bus for viewing. [Increment Address] -> [Load Data Bus]

- Deposit Next is the most complicated one. First, the data value on the front panel is written to the data bus, then the address is incremented, then the data bus value at this new address is loaded into the front panel's registers. [Deposit] -> [Increment Address] -> [Load Data Bus]

- Deposit is simple, and doesn't abide by the sequencing, allowing you to directly write a value from the front panel into RAM.

My understanding is that I'm performing Deposit Next backwards compared to an Altair 8800. Whereas the 8800 deposits that value into the location after the one you are currently viewing, mine deposits it into the current address you're viewing, then increments the address to show the value in there. This way if you're re-entering in data and don't wish to overwrite the value at that address, you can press Examine Next instead, and move on. Made a mistake, but only want to change a bit or two of that value, rather than all 8? You can do that too.

I hope I'm explaining this well enough. Feel free to ask whatever questions come to mind.